# LEGOAI: Auto-Scaling Large Model Training

A DISSERTATION PRESENTED

BY

SANKET JAYANT PURANDARE

TO

ENGINEERING AND APPLIED SCIENCES

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

IN THE SUBJECT OF

COMPUTER SCIENCE

HARVARD UNIVERSITY

CAMBRIDGE, MASSACHUSETTS

MAY 2025

©2025 – SANKET JAYANT PURANDARE

ALL RIGHTS RESERVED.

# LEGOAI: Auto-Scaling Large Model Training

## ABSTRACT

Training large AI models is computationally intensive. State-of-the-art language and vision models (LLMs and VLMs) often require thousands of GPUs and weeks or even months of training. As models scale to meet the demands of modern applications, efficient distributed training becomes essential, yet remains highly complex. No single distributed training configuration (or *training recipe*) works across all combinations of model architectures, hardware platforms, and data modalities. Practitioners must explore a vast configuration space through costly trial and error, often building and tuning implementations manually. Even then, out-of-memory errors and sub-optimal performance are common. This complexity is further compounded by the difficulty of synthesizing efficient implementations for selected configurations. Existing frameworks are fragmented across disparate libraries, lack interoperability, and are difficult to maintain, making the development, evaluation, and reuse of training recipes a significant engineering burden.

This thesis introduces LEGOAI, a system that transforms distributed AI training into an automated, scalable, and modular process. Given a model, dataset, and hardware configuration, LEGOAI automatically selects the optimal distributed training configuration and generates a production-ready implementation that scales to thousands of GPUs. At its core, LEGOAI serves as a synthesis engine: it decomposes state-of-the-art training strategies into modular, composable design principles and unifies them within a single coherent framework. In doing so, LEGOAI exposes a vast configuration space that comprises not only existing state-of-the-art algorithms but also entirely new designs

beyond them. Through high-fidelity simulation, it predicts memory usage and runtime without requiring execution, enabling fast and safe exploration of the configuration space. Finally, for the empirically optimal configuration, it synthesizes an efficient and scalable implementation. In addition to exploring, comparing, and deploying state-of-the-art algorithms, LEGOAI enables full-stack research by analyzing and synthesizing entirely new training algorithms derived from the design space through the composition of existing design principles.

We evaluate LEGOAI across diverse models, GPU types (A100, H100), and interconnects (Infini-Band, RoCE), demonstrating strong scalability, accurate simulation, and effective policy synthesis. LEGOAI achieves speedups of 65.08%, 12.59%, and 30% over optimized baselines on LLaMA 3.1 models at 128, 256, and 512 GPU scales, respectively. It predicts runtime with over 90% accuracy and memory usage with 99.9% accuracy across hardware configurations. To demonstrate LEGOAI's research capabilities, we synthesize new memory-efficient training algorithms based on recomputation that reduce overhead by up to 90% compared to baselines, while achieving superior compute-memory trade-offs by matching ILP-optimal solutions and running over  $100\times$  faster.

Thus, LEGOAI is the first system to unify the synthesis, simulation, and deployment of distributed training strategies, significantly reducing cost, complexity, and uncertainty while enabling broader and more efficient exploration of the large-scale AI training design space.

# Contents

|                                                                                                       |      |

|-------------------------------------------------------------------------------------------------------|------|

| TITLE PAGE                                                                                            | i    |

| COPYRIGHT                                                                                             | ii   |

| ABSTRACT                                                                                              | iii  |

| TABLE OF CONTENTS                                                                                     | v    |

| LISTING OF FIGURES                                                                                    | vii  |

| LISTING OF TABLES                                                                                     | x    |

| DEDICATION                                                                                            | xiii |

| ACKNOWLEDGEMENTS                                                                                      | xiv  |

| 1 INTRODUCTION                                                                                        | 1    |

| 1.1 Motivation . . . . .                                                                              | 1    |

| 1.2 Thesis Problem and Thesis Statement . . . . .                                                     | 7    |

| 1.3 TORCHTITAN: A Unified, Modular, Composable, and Scalable Distributed Training Framework . . . . . | 8    |

| 1.4 TORCHSIM: High Fidelity Runtime and Memory Estimation for Distributed Training . . . . .          | 11   |

| 1.5 AUTO-SAC: Enhancing the Compute–Memory Efficiency Trade-Off in Distributed Training . . . . .     | 14   |

| 1.6 Thesis Contributions . . . . .                                                                    | 16   |

| 1.7 Thesis Organization . . . . .                                                                     | 20   |

| 2 PRELIMINARIES                                                                                       | 21   |

| 2.1 Single-GPU Model Training . . . . .                                                               | 22   |

| 2.2 Communication Collectives . . . . .                                                               | 24   |

|      |                                                                                                |            |

|------|------------------------------------------------------------------------------------------------|------------|

| 2.3  | Distributed Model Training . . . . .                                                           | 25         |

| 2.4  | Distributed Training Execution Semantics . . . . .                                             | 35         |

| 2.5  | Distributed Model Training Paradigms . . . . .                                                 | 37         |

| 2.6  | Activation Checkpointing . . . . .                                                             | 38         |

| 3    | <b>TORCHTITAN: A UNIFIED, MODULAR, COMPOSABLE, AND SCALABLE DISTRIBUTED TRAINING FRAMEWORK</b> | <b>41</b>  |

| 3.1  | TORCHTITAN simple and modular end-to-end training pipeline . . . . .                           | 42         |

| 3.2  | Composable N-D parallelism training . . . . .                                                  | 43         |

| 3.3  | Optimizing training efficiencies . . . . .                                                     | 47         |

| 3.4  | Production ready training . . . . .                                                            | 49         |

| 3.5  | Experimentation . . . . .                                                                      | 51         |

| 3.6  | Scaling with TORCHTITAN 4D Parallelism . . . . .                                               | 56         |

| 3.7  | Related Work . . . . .                                                                         | 58         |

| 3.8  | Implementation Details . . . . .                                                               | 59         |

| 3.9  | Summary . . . . .                                                                              | 70         |

| 4    | <b>TORCHSIM: HIGH FIDELITY RUNTIME AND MEMORY ESTIMATION FOR DISTRIBUTED TRAINING</b>          | <b>71</b>  |

| 4.1  | Deriving TORCHSIM’s Design . . . . .                                                           | 73         |

| 4.2  | TORCHSIM Capture and Workflow . . . . .                                                        | 75         |

| 4.3  | TORCHSIM Memory Simulator . . . . .                                                            | 84         |

| 4.4  | TORCHSIM Compute Time Estimation Models . . . . .                                              | 91         |

| 4.5  | TORCHSIM Communication Time Estimation Models . . . . .                                        | 94         |

| 4.6  | TORCHSIM Runtime Simulator . . . . .                                                           | 103        |

| 4.7  | Experimental Results . . . . .                                                                 | 110        |

| 4.8  | Related Work . . . . .                                                                         | 126        |

| 4.9  | Future Directions . . . . .                                                                    | 131        |

| 4.10 | Summary . . . . .                                                                              | 132        |

| 5    | <b>AUTO-SAC: ENHANCING THE COMPUTE–MEMORY EFFICIENCY TRADE-OFF IN DISTRIBUTED TRAINING</b>     | <b>133</b> |

| 5.1  | Motivation and Key Insights . . . . .                                                          | 135        |

| 5.2  | AUTO-SAC: High-Level Design and Solution Overview . . . . .                                    | 138        |

| 5.3  | SAC Estimator . . . . .                                                                        | 142        |

| 5.4  | An ILP-Based Global per Module AC Budgeting Algorithm . . . . .                                | 146        |

| 5.5  | Greedy, Kapsack and ILP SAC Algorithms . . . . .                                               | 149        |

| 5.6  | Experimental Analysis . . . . .                                                                | 158        |

| 5.7  | Summary . . . . .                                                                              | 163        |

| 6    | <b>THESIS SUMMARY</b>                                                                          | <b>166</b> |

# Listing of figures

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

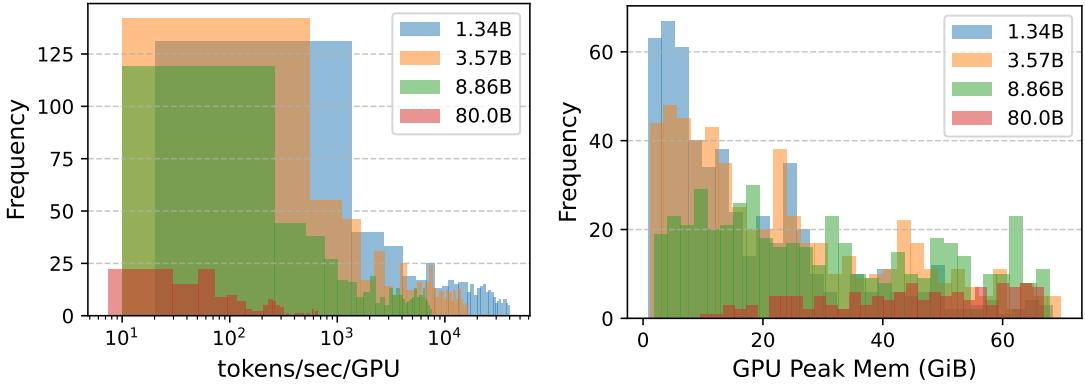

| 1.1 | Huggingface performance benchmarking of 1,728 out of 3,306 training runs reveals significant variance in throughput and peak memory consumption, highlighting the impact of training configurations. . . . .                                                                                                                                                                                                                                                                                                     | 5  |

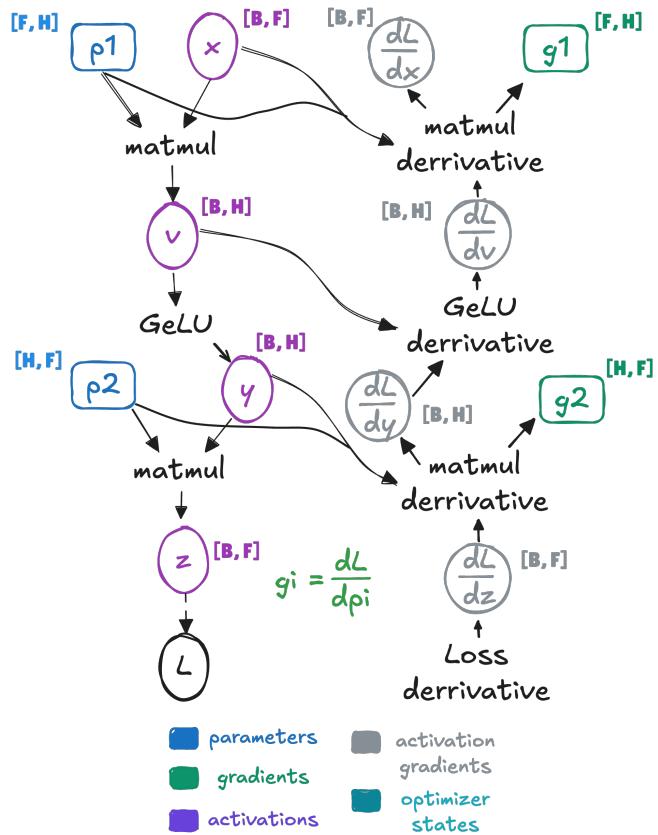

| 2.1 | Parameters, gradients, optimizer states and activations retained in memory during single GPU training. . . . .                                                                                                                                                                                                                                                                                                                                                                                                   | 23 |

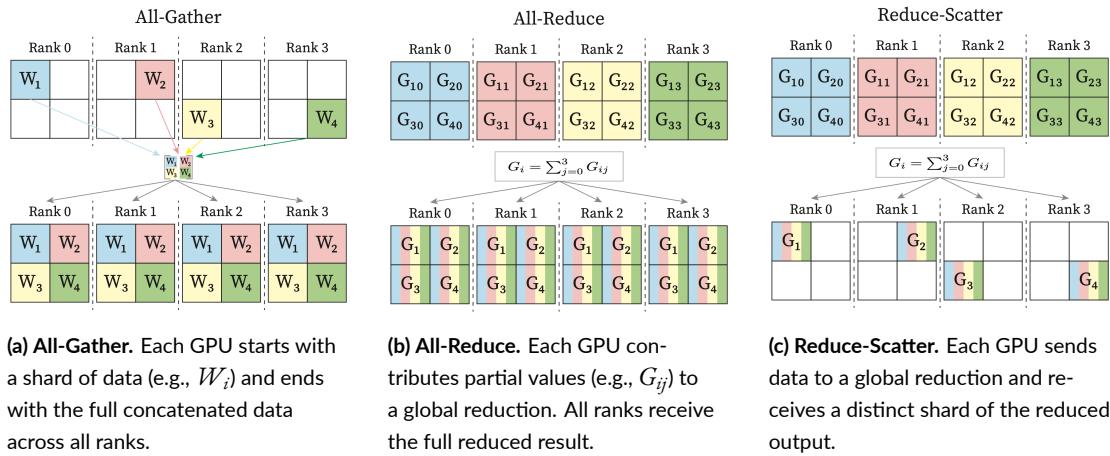

| 2.2 | Visual illustration of core collective communication primitives used in distributed training Kempner Institute (2025). These operations are fundamental to model parallelism and efficient synchronization across GPUs. . . . .                                                                                                                                                                                                                                                                                  | 24 |

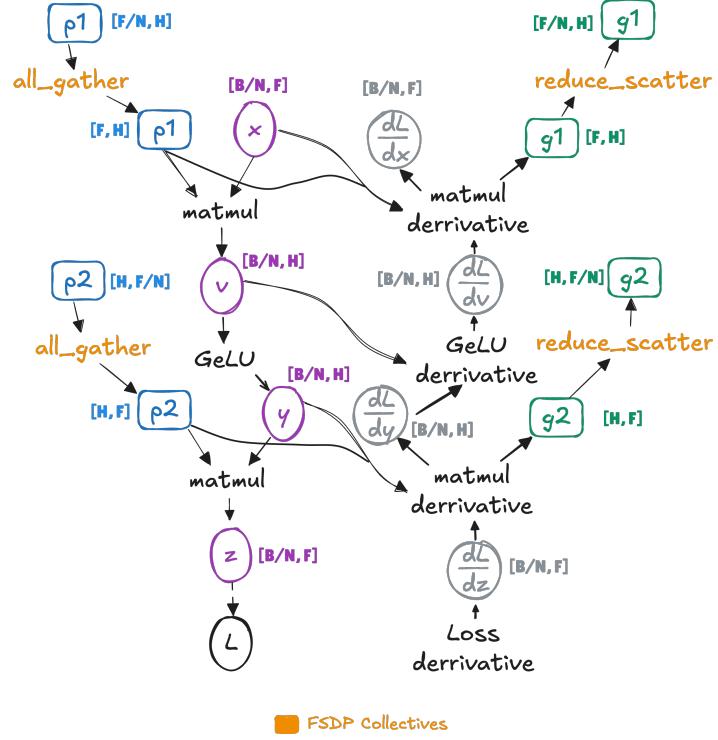

| 2.3 | FSDP shards the parameters, gradients and optimizer states across multiple GPUs. It reconstructs the parameters dynamically and averages and redistributes the gradients dynamically using the <i>all_gather</i> and <i>reduce_scatter</i> collective operations respectively. . . . .                                                                                                                                                                                                                           | 26 |

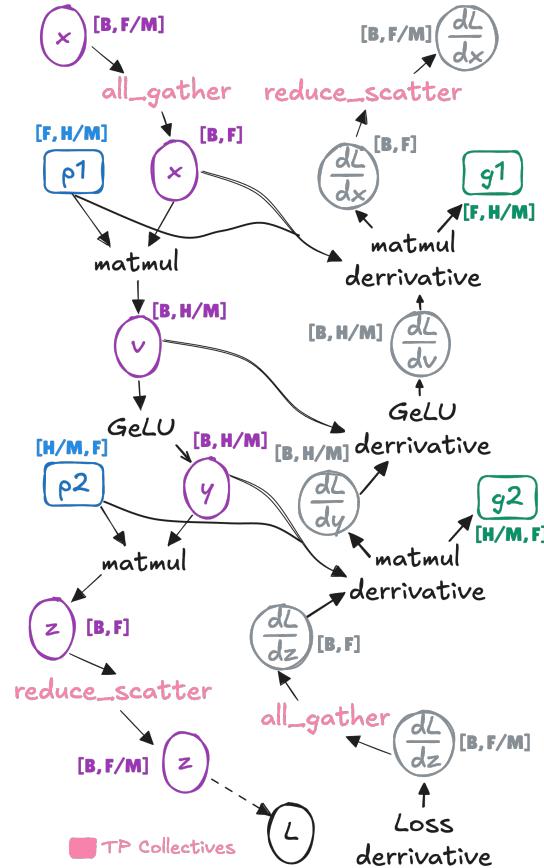

| 2.4 | Tensor Parallelism (TP) partitions the model parameters across GPUs along the hidden dimension: $p_1$ is split column-wise and $p_2$ row-wise. The input $x$ is sharded along the feature dimension and reconstructed using <i>all_gather</i> before the forward pass. Intermediate activations remain sharded, and the final output is redistributed using <i>reduce_scatter</i> . TP reduces memory usage for parameters, gradients, and activations, while avoiding full <i>all_reduce</i> overheads. . . . . | 28 |

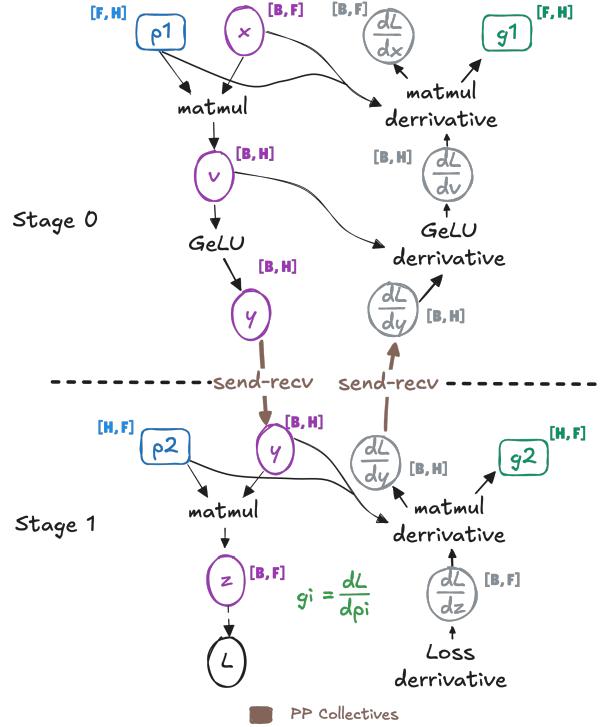

| 2.5 | Pipeline Parallelism (PP) partitions the model into sequential stages, each assigned to a different GPU or GPU group. Intermediate activations and gradients are transferred between stages using <i>send/recv</i> collectives. Each stage executes forward and backward computations independently, enabling concurrent microbatch execution and efficient scaling across deep models. . . . .                                                                                                                  | 31 |

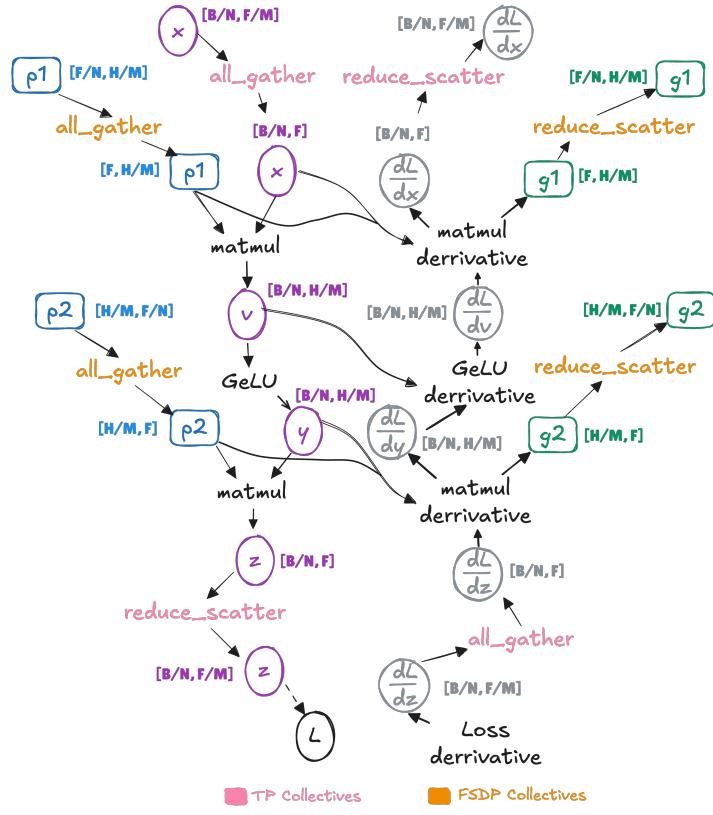

| 2.6 | 2D Parallelism combines Fully Sharded Data Parallelism (FSDP) and Tensor Parallelism (TP) to reduce memory and distribute computation. Parameters and optimizer states are sharded across FSDP groups, while TP partitions the model layers along the hidden dimension. Inputs are sharded across the feature dimension and reconstructed using <i>all_gather</i> , while outputs are redistributed using <i>reduce_scatter</i> . Gradients are locally reduced via FSDP and TP collectives. . . . .             | 32 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

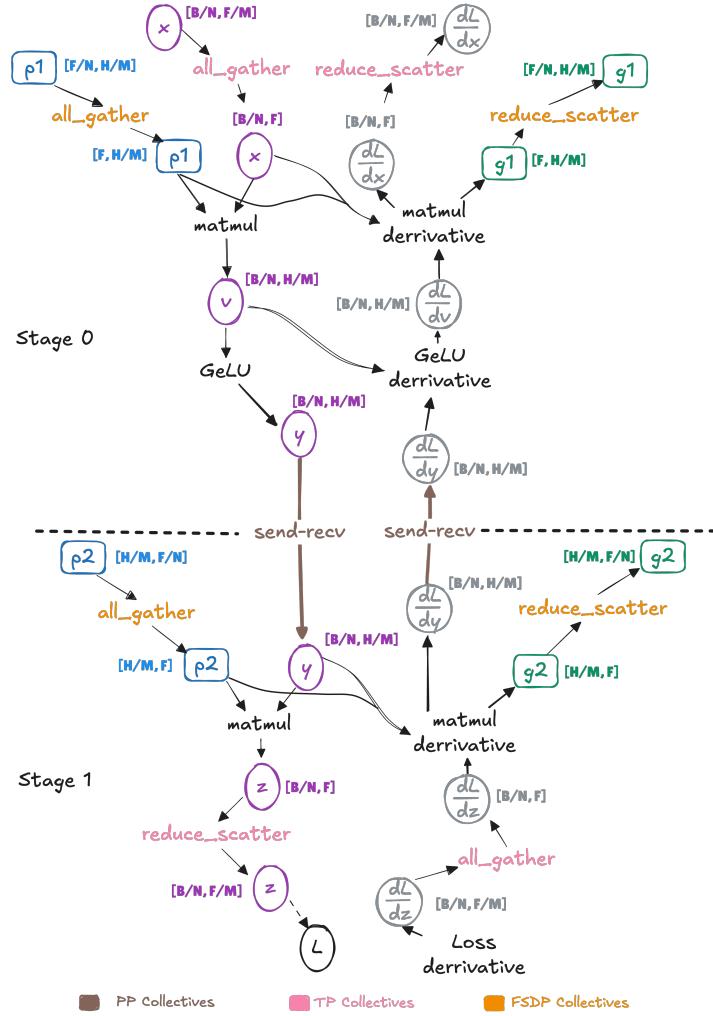

| 2.7  | 3D Parallelism integrates Pipeline Parallelism (PP), Tensor Parallelism (TP), and Fully Sharded Data Parallelism (FSDP) to enable scalable and memory-efficient training across thousands of GPUs. Each pipeline stage applies TP to shard computation along the hidden dimension, and FSDP to shard parameters within TP subgroups. <i>send/recv</i> operations are used for inter-stage communication, while <i>all_gather</i> and <i>reduce_scatter</i> are used to manage intra-stage computation and memory efficiency. . . . . | 34  |

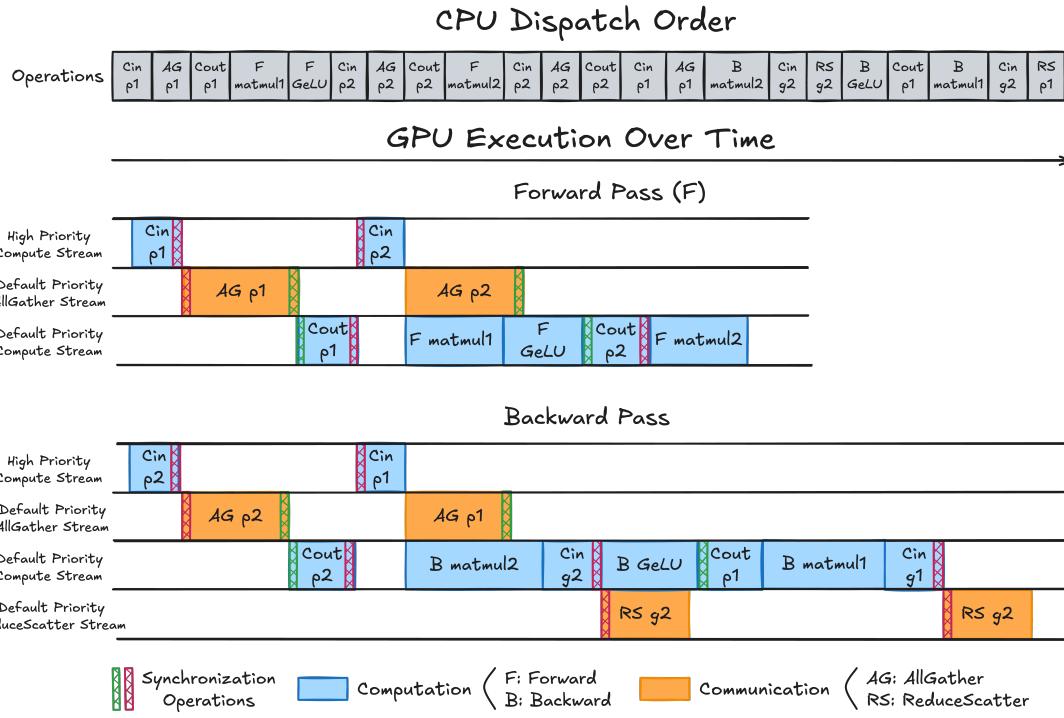

| 2.8  | The operators (blue) and communication collectives (orange) dispatched by the CPU across multiple GPU streams for the example in 2.3. Although the CPU issues operations sequentially, streams can overlap in execution, e.g., as shown by <i>Cin_p2</i> and <i>AG_p2</i> in the forward pass, until forced to synchronize, e.g. by <i>all_gather</i> (AG) and <i>reduce_scatter</i> (RS), as denoted by the red and green vertical lines. . . . .                                                                                   | 35  |

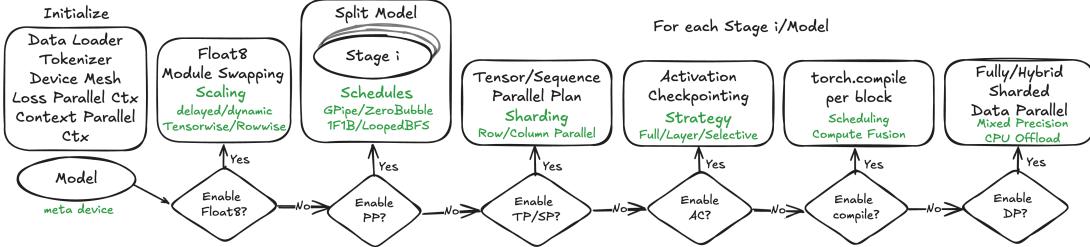

| 3.1  | Composable and Modular TORCHTITAN initialization workflow. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43  |

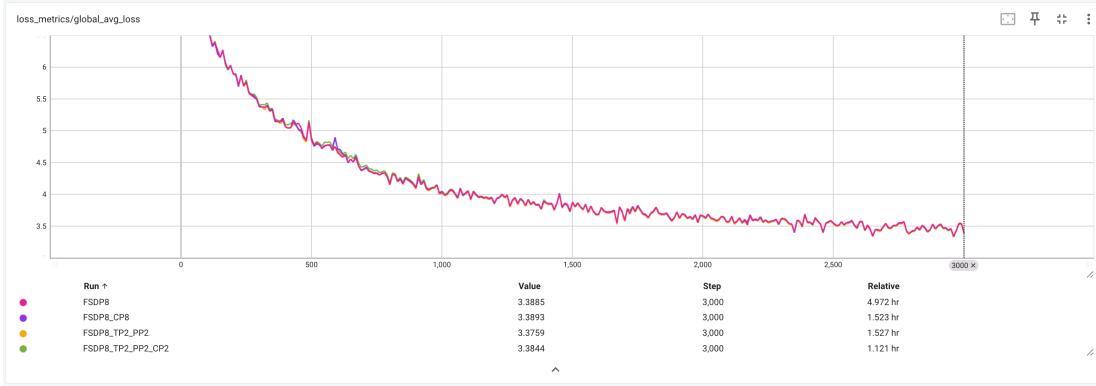

| 3.2  | Loss converging tests on Llama 3.1 8B. C4 dataset. Local batch size 4, global batch size 32. 3000 steps, 600 warmup steps. . . . .                                                                                                                                                                                                                                                                                                                                                                                                   | 56  |

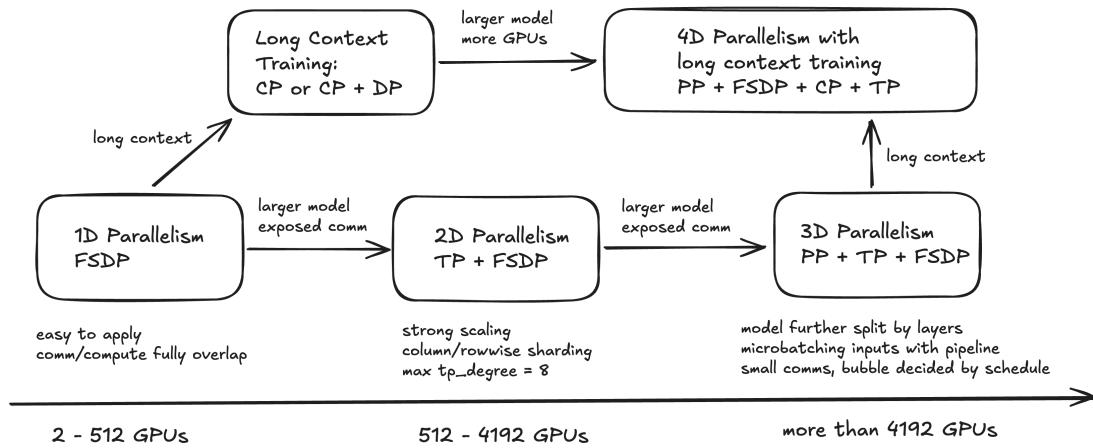

| 3.3  | Scaling with 4D Parallelism . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56  |

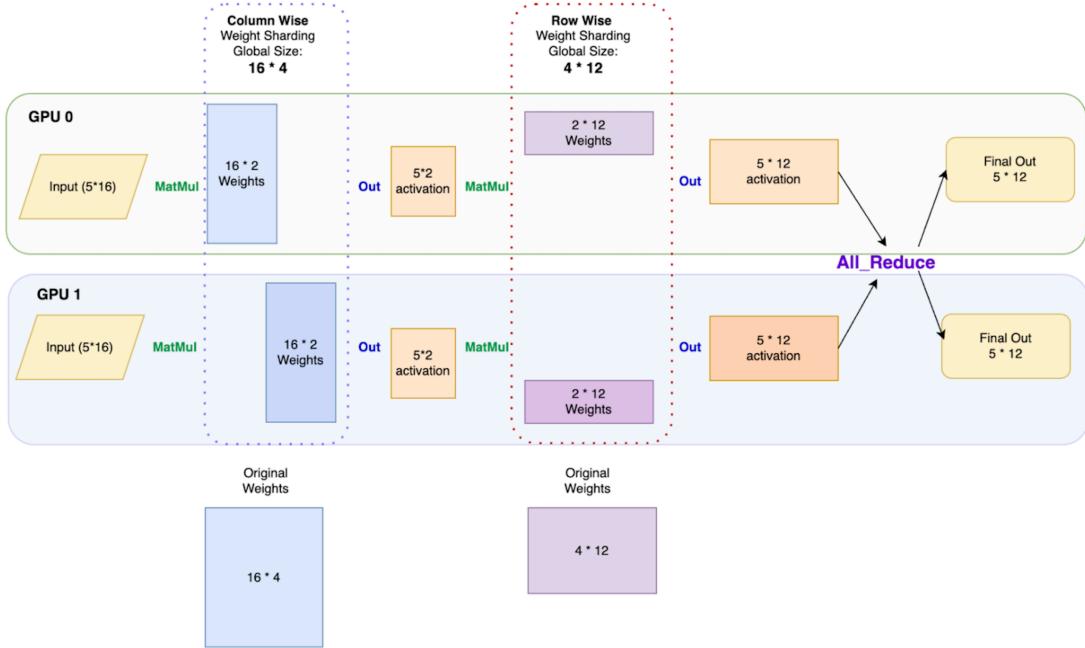

| 3.4  | Tensor Parallel in detail (2 GPUs, data moves from left to right). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 67  |

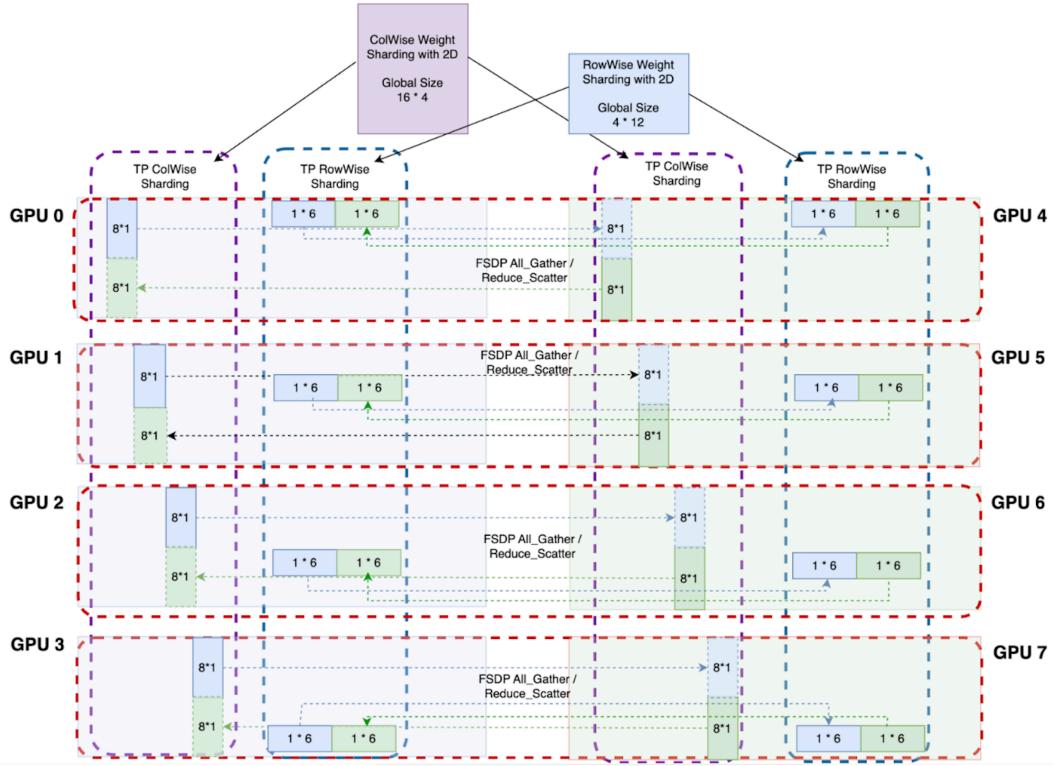

| 3.5  | FSDP2 + Tensor Parallel (TP degree 4) sharding layout, with 2 nodes of 4 GPUs. .                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68  |

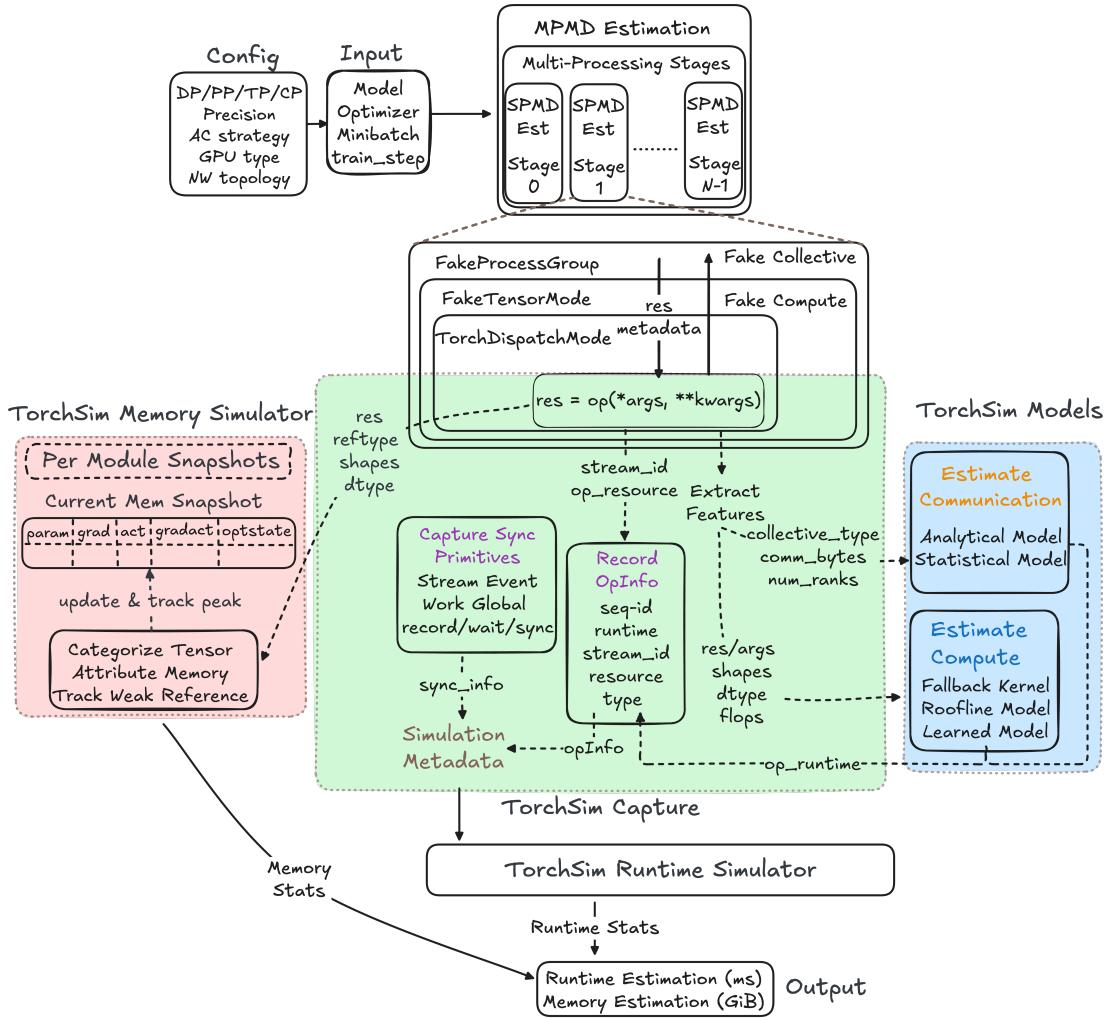

| 4.1  | TORCHSIM: High-level System Design . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75  |

| 4.2  | Actual and Fake Tensor Representation. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 76  |

| 4.3  | TORCHSIM design internals for capturing tensor, operator, and synchronization primitive metadata to enable precise memory and runtime estimation. . . . .                                                                                                                                                                                                                                                                                                                                                                            | 82  |

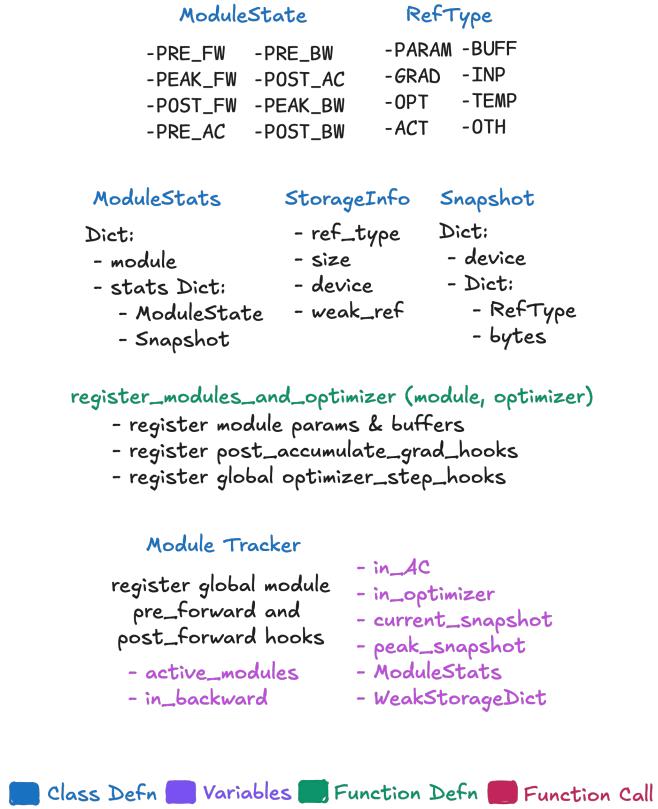

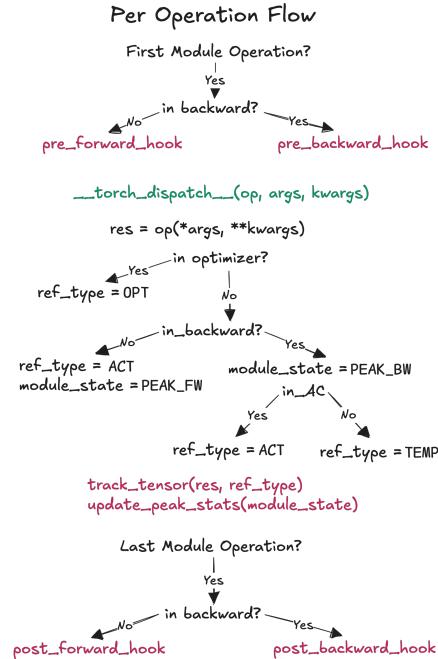

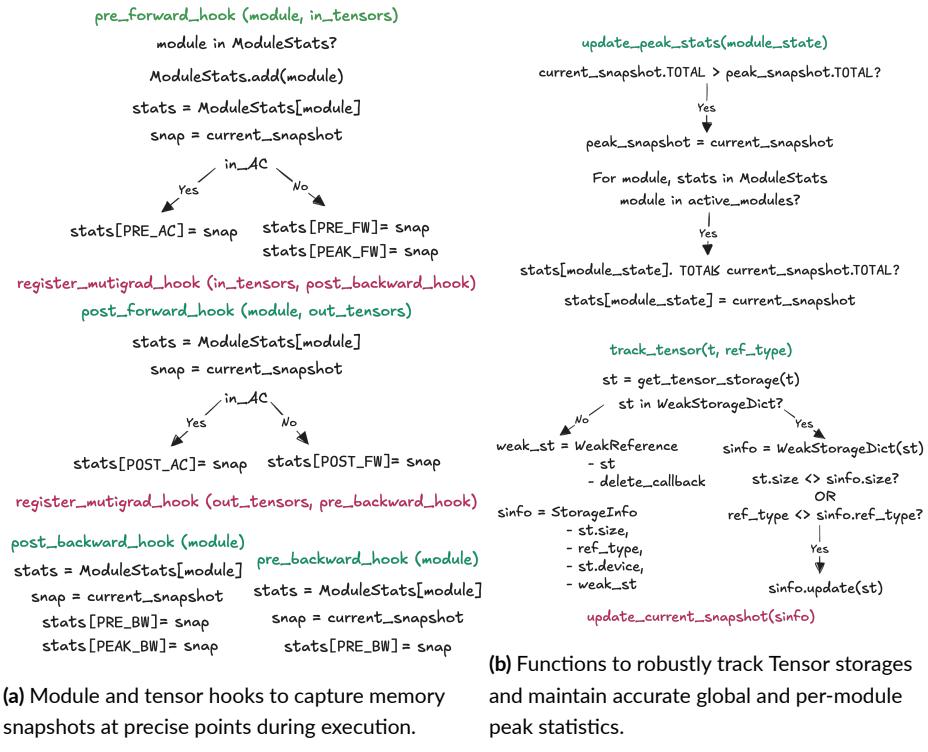

| 4.4  | Memory Simulator’s data structures and functions for estimating, tracking, attributing and categorizing memory usage . . . . .                                                                                                                                                                                                                                                                                                                                                                                                       | 87  |

| 4.5  | Extending <i>RefTypes</i> and <i>ModuleStates</i> for distributed training . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88  |

| 4.6  | Memory Simulator Workflow . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90  |

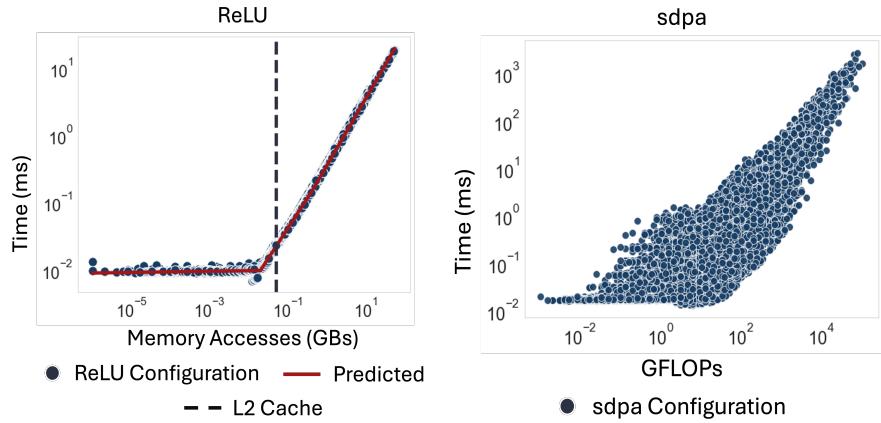

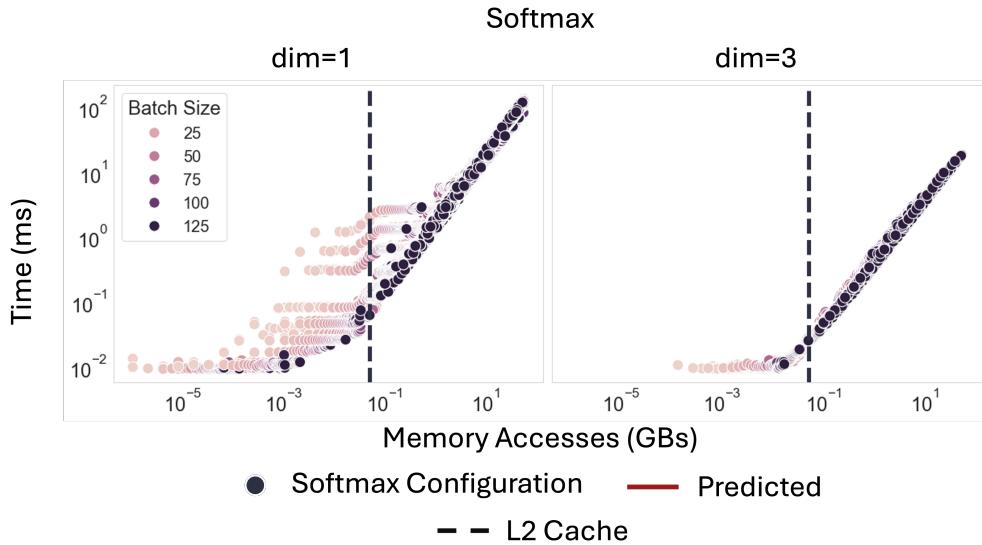

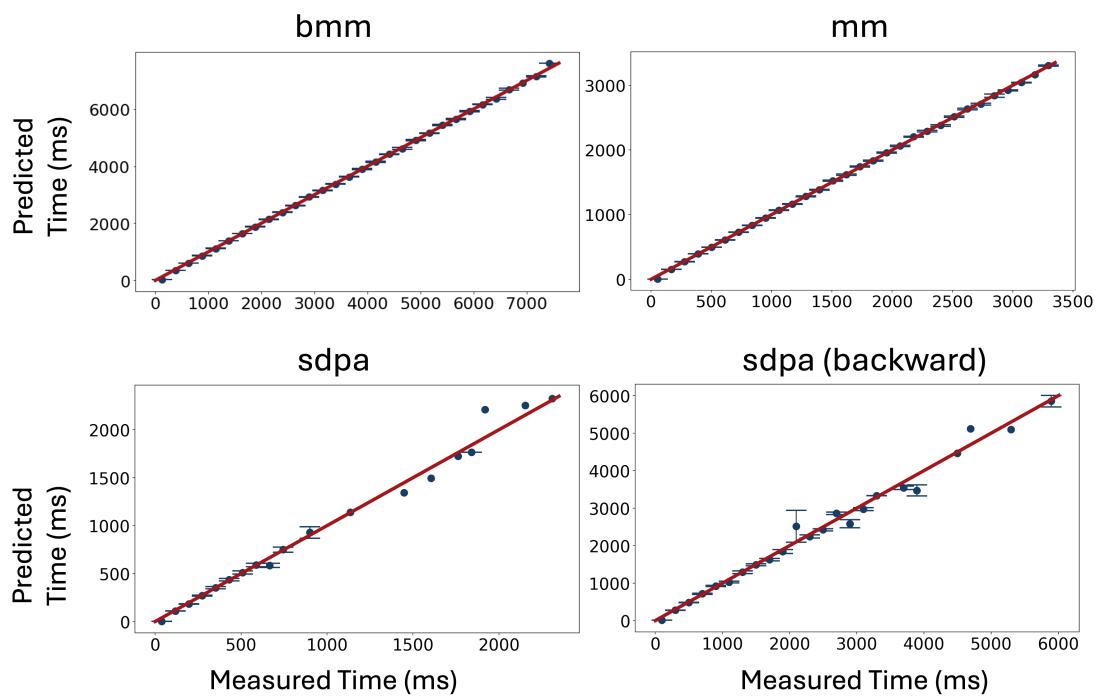

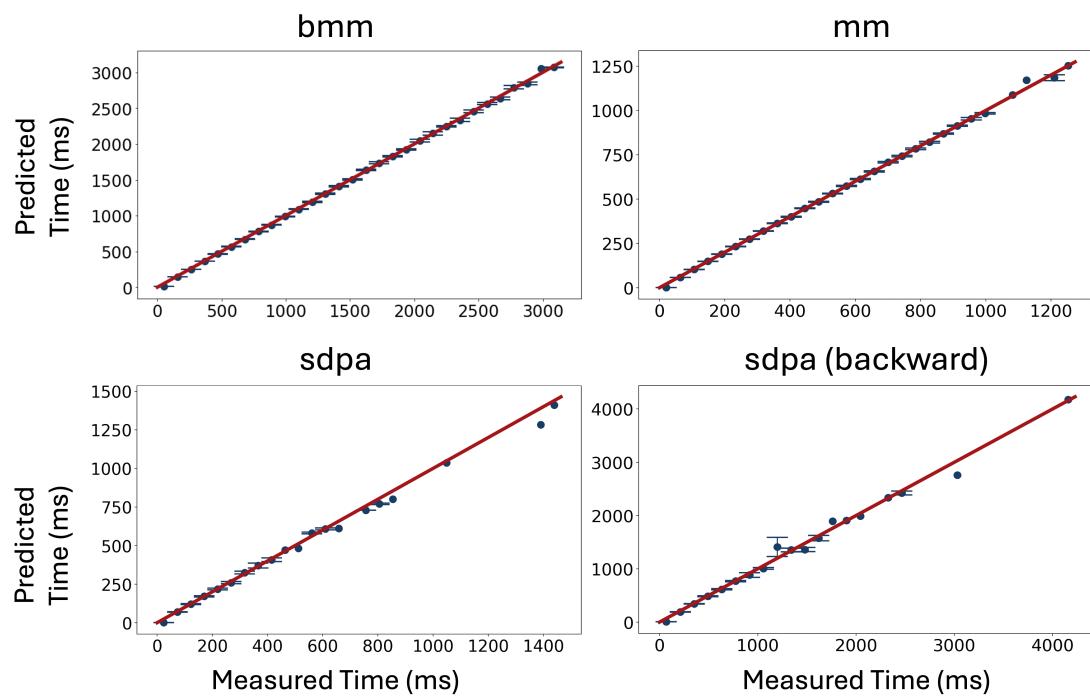

| 4.7  | The Runtimes for Different Operator Categories . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 92  |

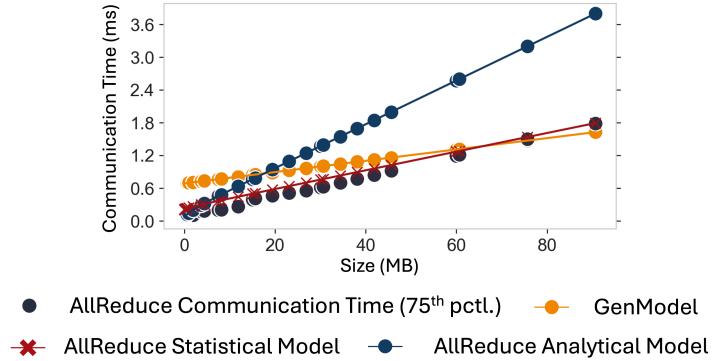

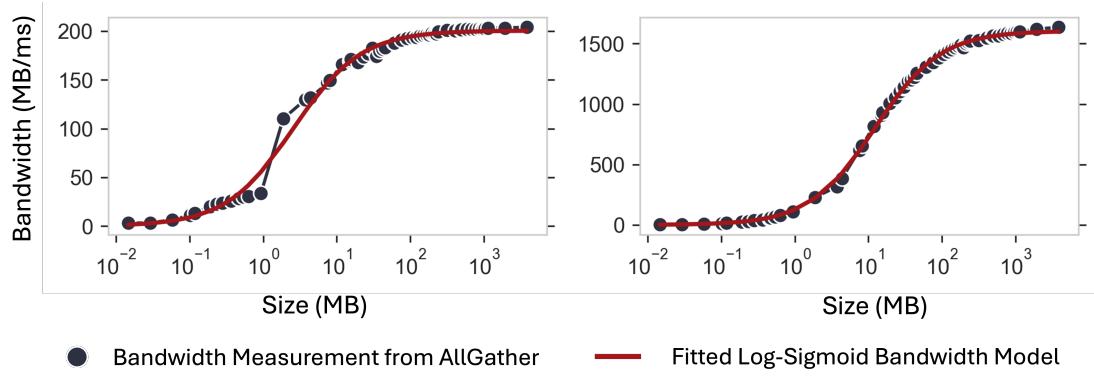

| 4.8  | Insights from benchmarking inter-GPU communication . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 95  |

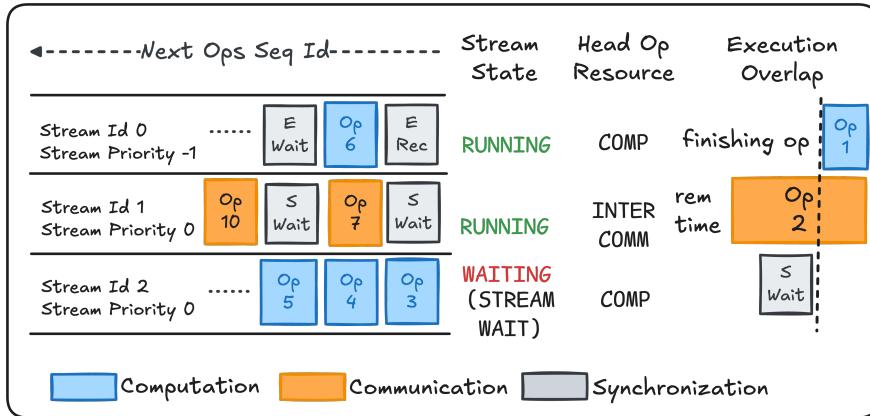

| 4.9  | TORCHSIM Runtime Simulator in action. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107 |

| 4.10 | The predicted runtime plotted against the measured runtime for the operators on NVIDIA A100s. The red line denotes the line $y = x$ . We binned measured runtimes and took a mean per bin. . . . .                                                                                                                                                                                                                                                                                                                                   | 111 |

| 4.11 | The predicted runtime plotted against the measured runtime for the operators on NVIDIA H100s. The red line denotes the line $y = x$ . We binned measured runtimes and took a mean per bin. . . . .                                                                                                                                                                                                                                                                                                                                   | 112 |

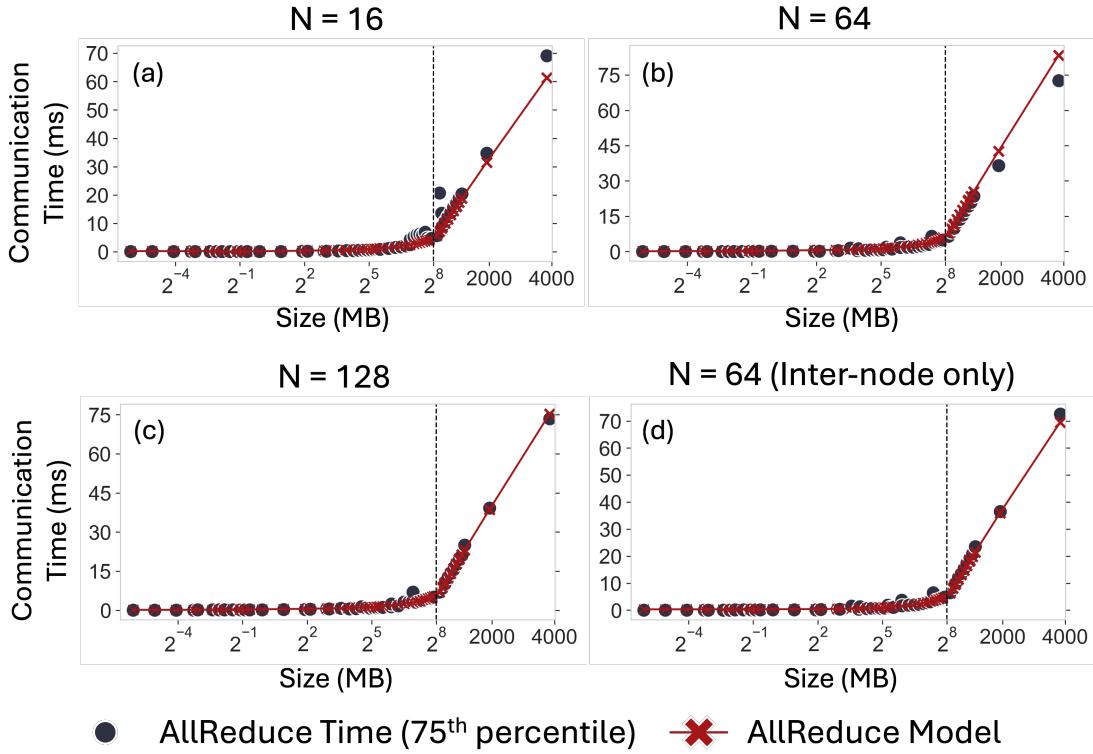

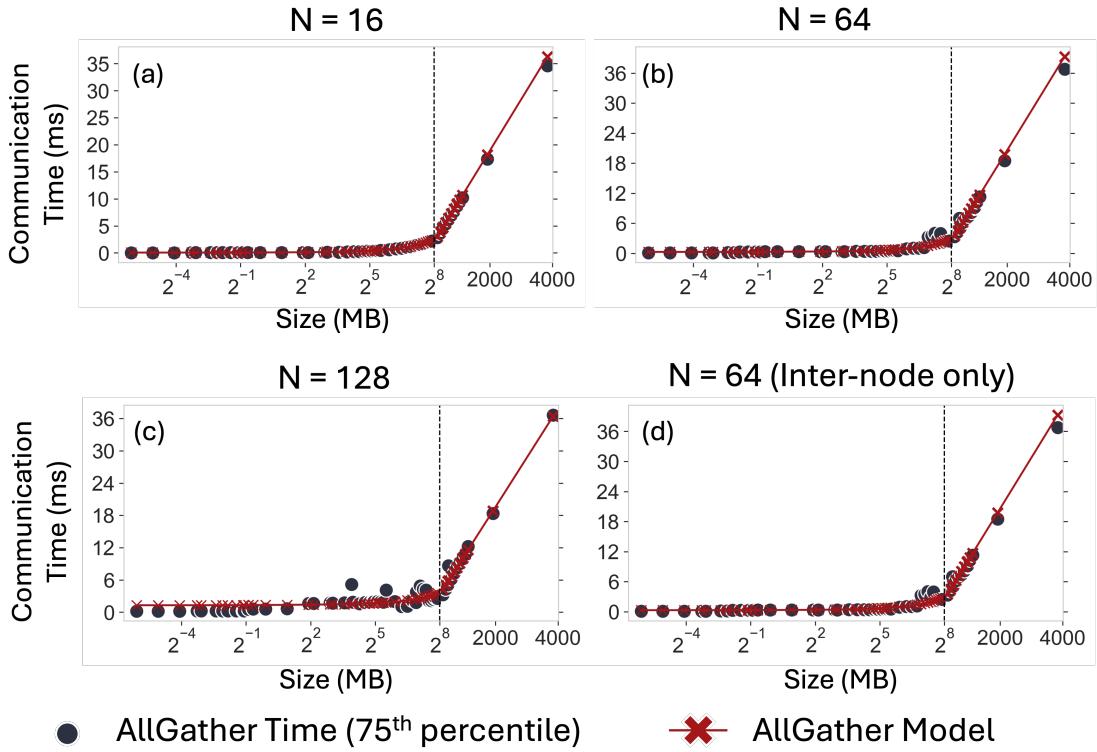

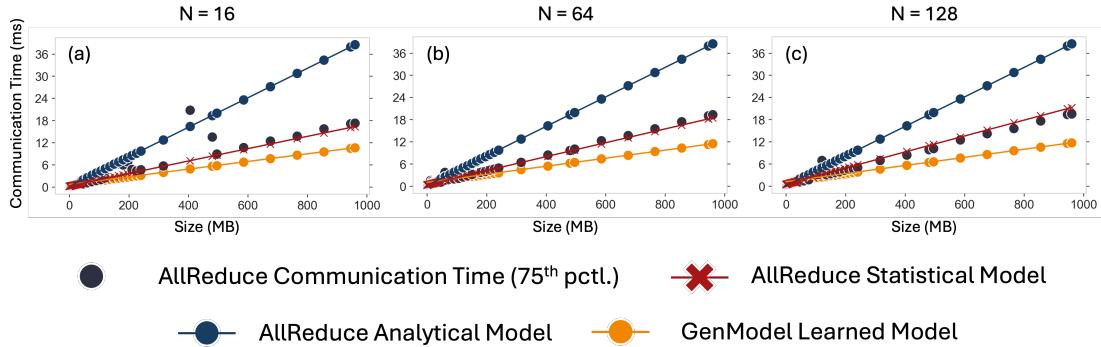

| 4.12 | 75th percentile AllReduce communication time from benchmarking data and predictions by the collective communication prediction model for each data size on cluster X. (a)–(c) show data from world sizes of $N = 16, 64, 128$ for 1D parallelism whereas (d) shows data for 2D parallelism for $N = 64$ . . . . .                                                                                                                                                                                                                    | 114 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.13 | 75th percentile AllGather communication time from benchmarking data and predictions by the collective communication prediction model for each data size on cluster X. Data size refers to the size of the output tensor in the AllGather operation, since the communication overhead scales with the output dimensions. (a)–(c) show data from world sizes of $N = 16, 64, 128$ for 1D parallelism whereas (d) shows data for 2D parallelism for $N = 64$ . . . . . | 115 |

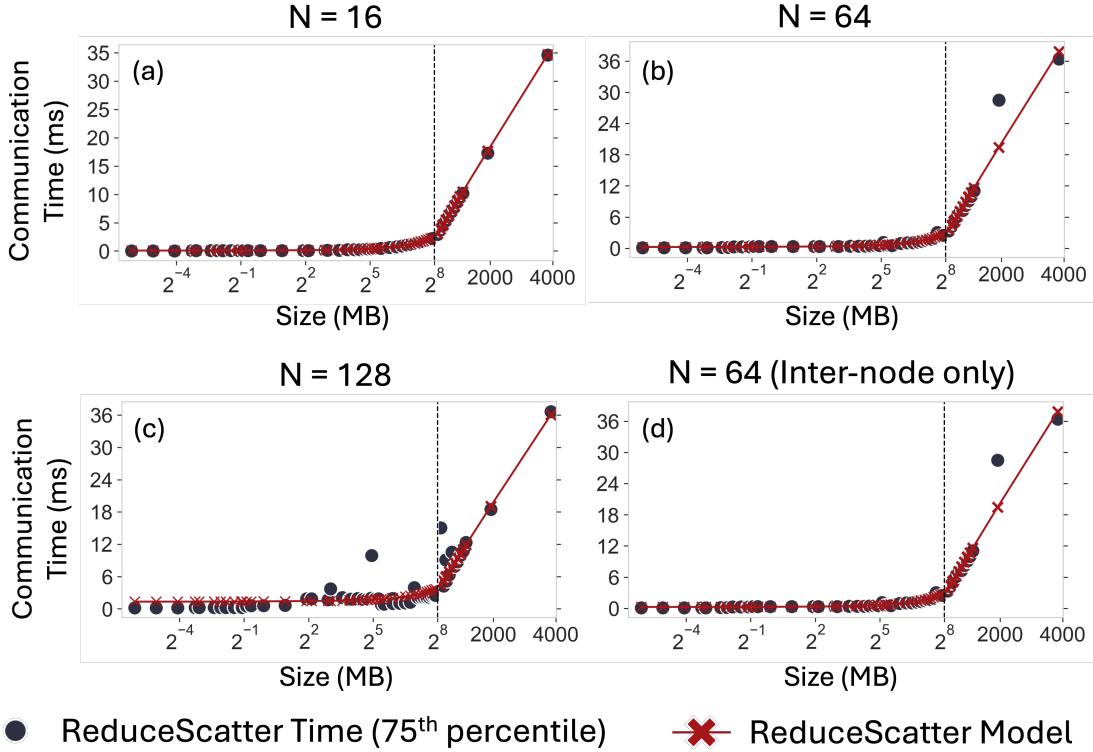

| 4.14 | 75th percentile ReduceScatter communication time from benchmarking data and predictions by the collective communication prediction model for each data size on cluster X, with the same log-linear scale as Figure 4.12. (a)–(c) show data from world sizes of $N = 16, 64, 128$ for 1D parallelism whereas (d) shows data for 2D parallelism for $N = 64$ . . . . .                                                                                                | 116 |

| 4.15 | 75th percentile AllReduce collective times on cluster X with predictions by the statistical communication model and the GenModel baseline predictions for 2D parallelism on $N = 16, 64, 128$ GPUs. . . . .                                                                                                                                                                                                                                                         | 117 |

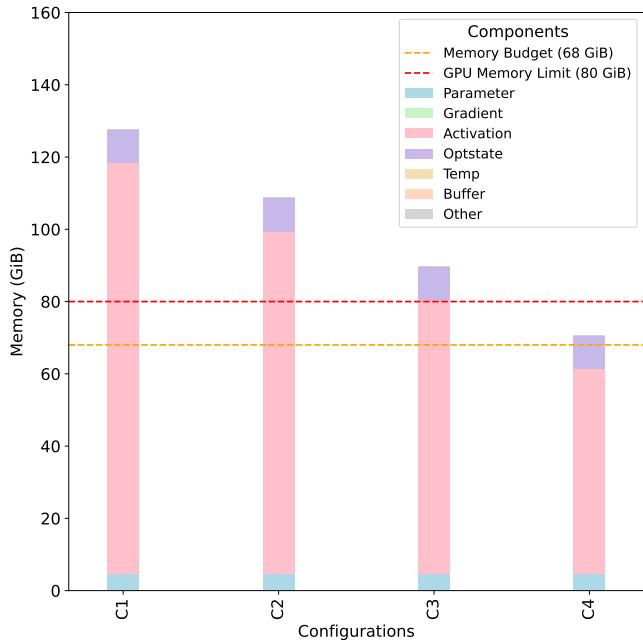

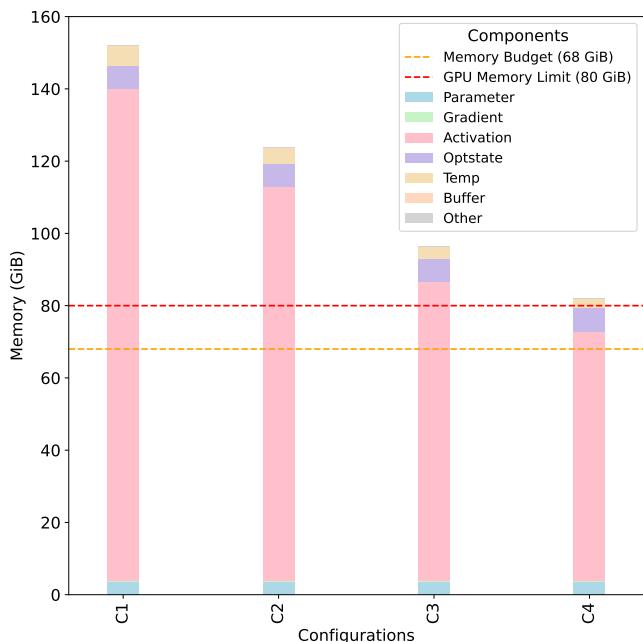

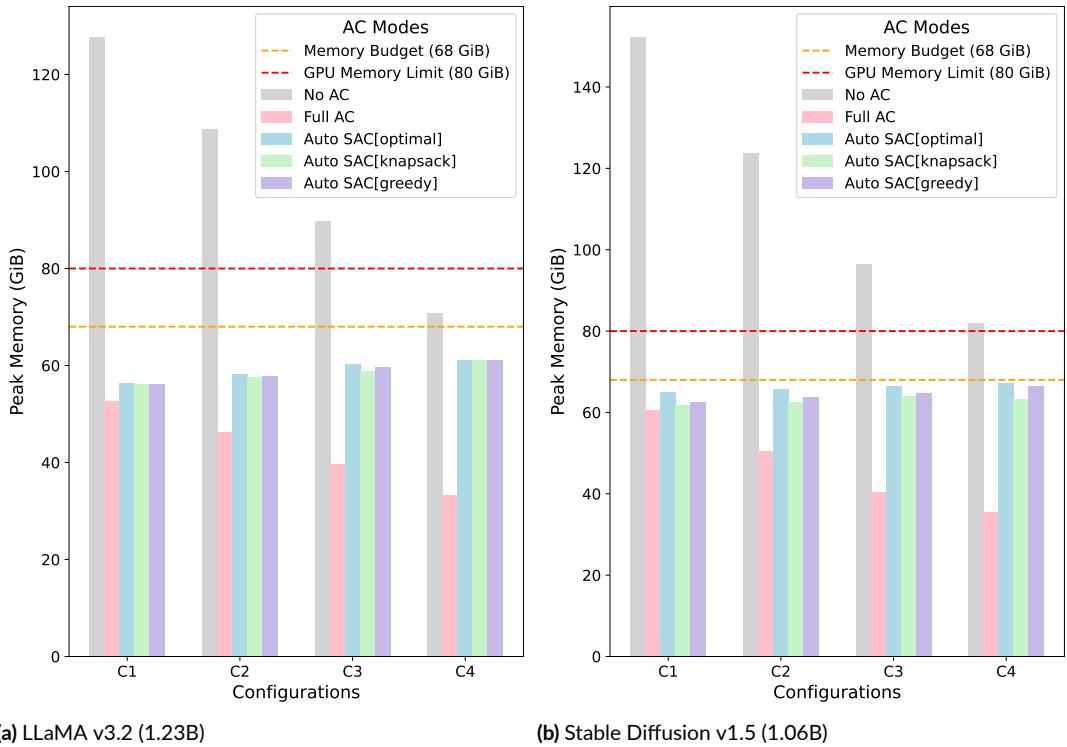

| 5.1  | Peak memory breakdown across configurations. Activations dominate memory usage in both LLM and diffusion models. . . . .                                                                                                                                                                                                                                                                                                                                            | 136 |

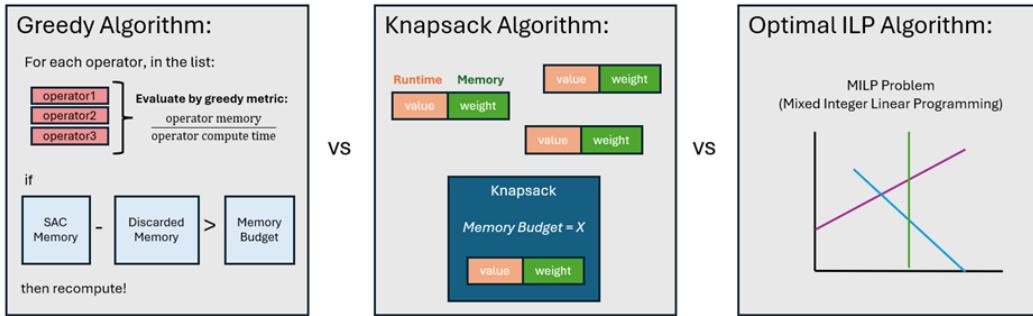

| 5.2  | Local SAC policy generation strategies: greedy, knapsack, and ILP. All methods take a module-specific memory discard target as input and output an operator-level recomputation policy. . . . .                                                                                                                                                                                                                                                                     | 142 |

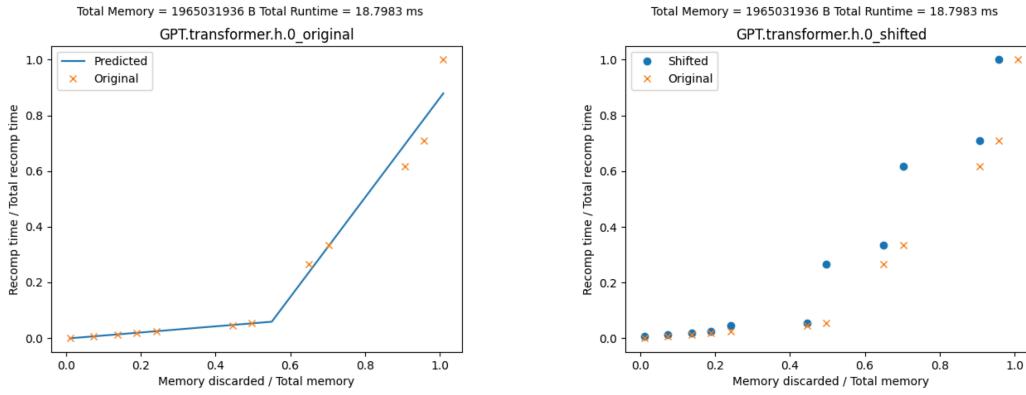

| 5.3  | SAC Estimator outputs for a Transformer module in GPT-2. . . . .                                                                                                                                                                                                                                                                                                                                                                                                    | 144 |

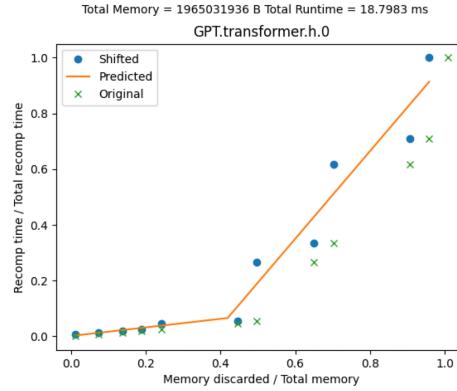

| 5.4  | From raw trade-off data to upper-bound approximation for GPT-2 Transformer module. . . . .                                                                                                                                                                                                                                                                                                                                                                          | 146 |

| 5.5  | Peak memory under various strategies. AUTO-SAC nearly saturates the budget while Full AC underutilizes memory due to lack of constraint awareness. . . . .                                                                                                                                                                                                                                                                                                          | 160 |

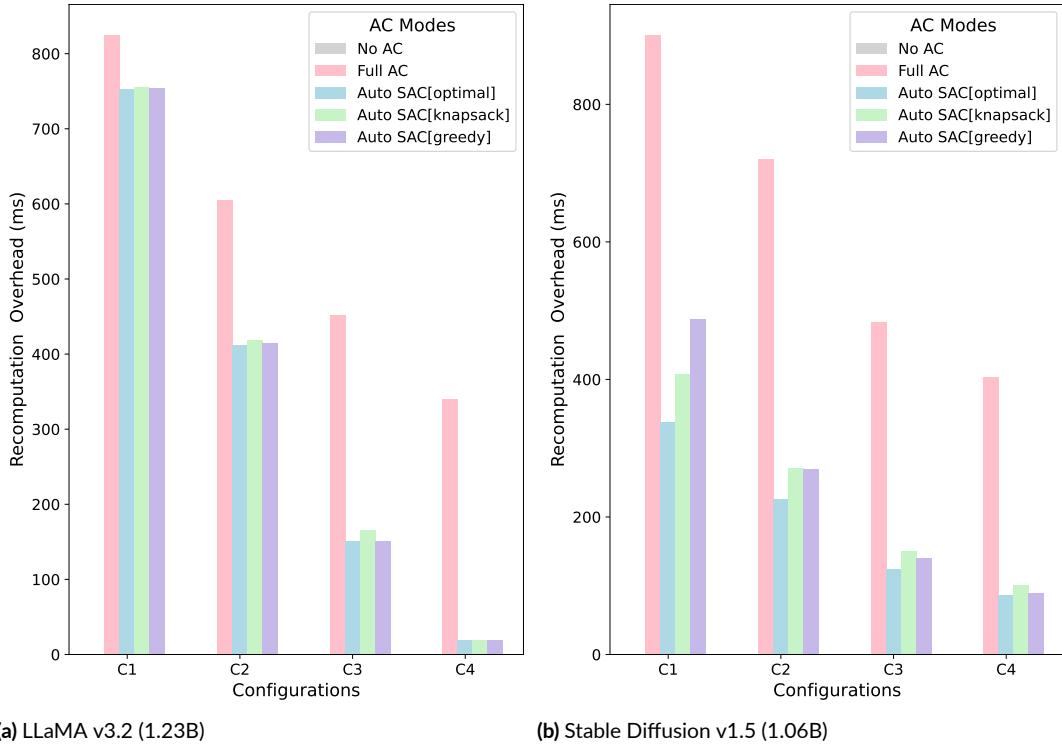

| 5.6  | Recomputation overhead under each strategy. AUTO-SAC consistently outperforms Full AC. Greedy and Knapsack are close to optimal. . . . .                                                                                                                                                                                                                                                                                                                            | 161 |

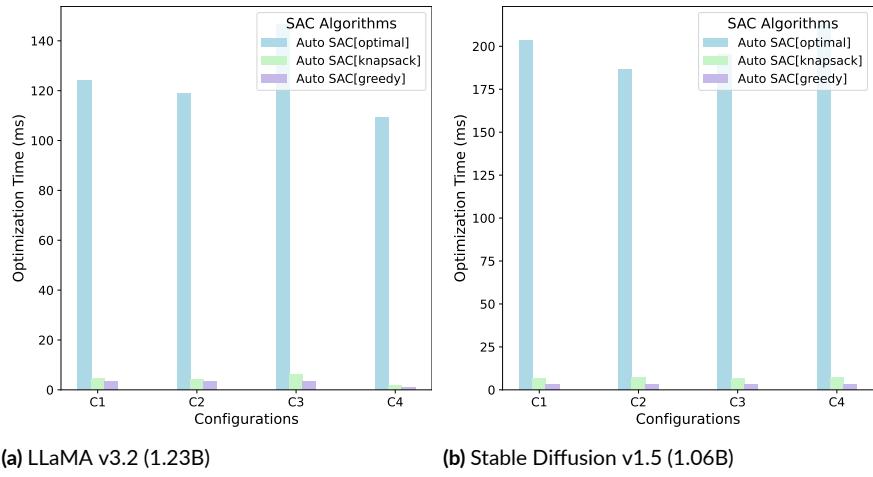

| 5.7  | Optimization time per solver. Greedy and Knapsack are $100\times$ faster than Optimal (ILP). . . . .                                                                                                                                                                                                                                                                                                                                                                | 162 |

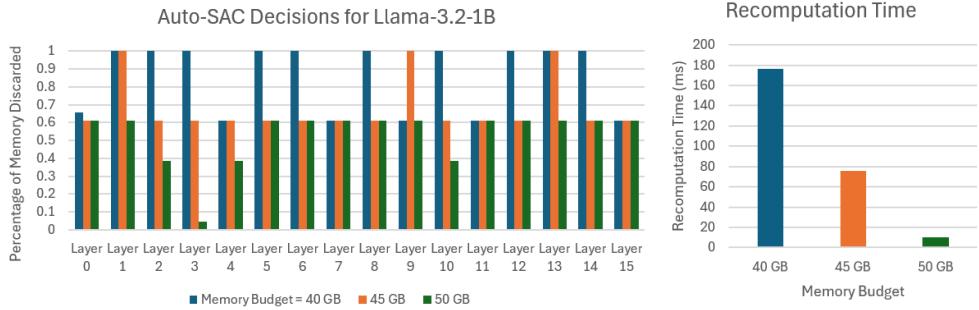

| 5.8  | AUTO-SAC ILP decisions and recomputation times across memory budgets for LLaMA v3.2-1B. As budgets increase, fewer activations are discarded, reducing recomputation. . . . .                                                                                                                                                                                                                                                                                       | 162 |

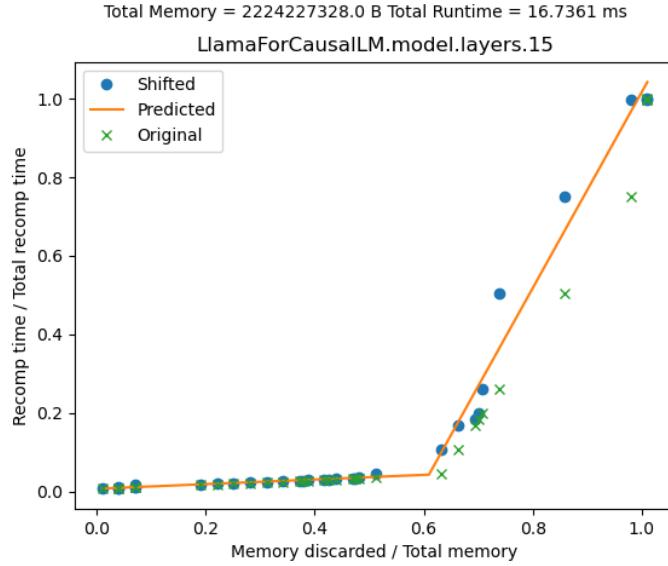

| 5.9  | Compute–memory trade-off curve for Layer 15 in LLaMA v3.2-1B. Discarding 60% of memory leads to <5% recomputation overhead. . . . .                                                                                                                                                                                                                                                                                                                                 | 164 |

# List of Tables

|     |                                                                                                                                                                                                                                                                                             |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Cost and experiment counts per model size (in k\$) for 3,306 experiments, resulting in a total estimated cost of \$469.17K . . . . .                                                                                                                                                        | 4  |

| 3.1 | 1D parallelism (FSDP) on Llama 3.1 8B model, 8 GPUs. Mixed precision training. Selective activation checkpointing. Local batch size 2, global batch size 16. (Stats per GPU) . . . . .                                                                                                      | 53 |

| 3.2 | 1D parallelism (FSDP) on Llama 3.1 8B model, 128 GPUs. Mixed precision training. Selective activation checkpointing. Local batch size 2, global batch size 256. (Stats per GPU) . . . . .                                                                                                   | 54 |

| 3.3 | 2D parallelism (FSDP + TP) + <code>torch.compile</code> + Float8 on Llama 3.1 70B model, 256 GPUs. Mixed precision training. Full activation checkpointing. FSDP degree 32, TP degree 8. Local batch size 16, global batch size 512. (Stats per GPU) . . . . .                              | 54 |

| 3.4 | 3D parallelism (FSDP + TP + PP) + <code>torch.compile</code> + Float8 + AsyncTP on Llama 3.1 405B model, 512 GPUs. Mixed precision training. Full activation checkpointing. FSDP degree 4, TP degree 8, PP degree 16. Local batch size 32, global batch size 128. (Stats per GPU) . . . . . | 54 |

| 3.5 | FSDP + CP + <code>torch.compile</code> + Float8 on Llama 3.1 8B model, 8 GPUs. Mixed precision training. Full activation checkpointing. Local batch size 1. (Stats per GPU) . . . . .                                                                                                       | 54 |

| 3.6 | 4D parallelism (FSDP + TP + PP + CP) + <code>torch.compile</code> + Float8 + AsyncTP + 1F1B on Llama 3.1 405B model, 512 GPUs. Mixed precision training. Full activation checkpointing. TP degree 8, PP degree 8. Local batch size 8. (Stats per GPU) . . . . .                             | 55 |

| 3.7 | Loss-converging tests setup. . . . .                                                                                                                                                                                                                                                        | 55 |

| 3.8 | Comparison of TORCHTITAN with Megatron-LM, DeepSpeed, and veScale with respect to parallelism, compiler support, activation checkpointing, and model checkpointing. . . . .                                                                                                                 | 60 |

| 3.9 | Lines of Code (LOC) comparison across systems. . . . .                                                                                                                                                                                                                                      | 60 |

| 4.1 | Enumeration classes representing the Resources, Queue states and Synchronization actions for primitives. . . . .                                                                                                                                                                            | 79 |

| 4.2 | Classes describing the Synchronization, Operator, Queue, and Simulator Metadata. . . . .                                                                                                                                                                                                    | 80 |

| 4.3 | Synchronization primitives with PyTorch semantics and detailed actions captured by TORCHSIM. . . . .                                                                                                                                                                                        | 81 |

|      |                                                                                                                                                                                                                                                                                                                        |     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.4  | List of Symbols for Communication Modeling . . . . .                                                                                                                                                                                                                                                                   | 97  |

| 4.5  | Analytical Cost Models for Collective Communication Algorithms . . . . .                                                                                                                                                                                                                                               | 97  |

| 4.6  | Process_Sync_Events for a given syncInfo and Q . . . . .                                                                                                                                                                                                                                                               | 109 |

| 4.7  | Regression and Accuracy Results for the Learned Compute-Bound Model on H100s                                                                                                                                                                                                                                           | 110 |

| 4.8  | Regression and Accuracy Results for the Learned Model on A100s. . . . .                                                                                                                                                                                                                                                | 110 |

| 4.9  | Root Mean Squared Error (RMSE) of Collective Communication Model and Gen-Model on Cluster X and Y. Baseline performance data from GenModel are shown for AllReduce in 2D parallelism only using an approximation of the Recursive Halving-Doubling model, since GenModel can only predict non-hierarchical AllReduce . | 118 |

| 4.10 | Model configurations used in single device simulator experiments. . . . .                                                                                                                                                                                                                                              | 119 |

| 4.11 | Runtime Simulator Accuracy Across Cost Models for Configurations of Deep Learning Models . . . . .                                                                                                                                                                                                                     | 121 |

| 4.12 | Runtime simulator accuracy for 1D FSDP across 128 GPUs for Llama 3 70B training. We achieve a mean accuracy of 90% in predicting iteration time while incurring minimal prediction overhead (shown in the final column). . . . .                                                                                       | 122 |

| 4.13 | Runtime simulator accuracy for 2D FSDP across 128 GPUs for Llama 3 70B training. We achieve a mean accuracy of 91% in predicting iteration time while incurring minimal prediction overhead (shown in the final column). . . . .                                                                                       | 122 |

| 4.14 | Memory usage estimates and actual for various models and configurations. Memory Simulator achieves approximately 99% accuracy in all scenarios across the 7 models with different batch sizes, sequence lengths, precisions and memory optimizations techniques like activation checkpointing. . . . .                 | 124 |

| 4.15 | Memory Simulator achieves $\geq 99\%$ accuracy with distributed 1D FSDP training and is able to get the estimation within 30 seconds for Llama 70 billion model. . . . .                                                                                                                                               | 125 |

| 4.16 | Memory Simulator achieves $\geq 99\%$ accuracy with distributed 2D FSDP+TP training and is able to get the estimation within 30 seconds for Llama 70 billion model.                                                                                                                                                    | 125 |

| 5.1  | Variables used in the global ILP formulation . . . . .                                                                                                                                                                                                                                                                 | 147 |

| 5.2  | Symbols used in the greedy SAC algorithm . . . . .                                                                                                                                                                                                                                                                     | 150 |

| 5.3  | Symbols used in the knapsack SAC algorithm . . . . .                                                                                                                                                                                                                                                                   | 152 |

| 5.4  | Symbols used in the ILP-based SAC algorithm . . . . .                                                                                                                                                                                                                                                                  | 156 |

| 5.5  | Configuration details for Stable Diffusion and LLaMA v3.2-1B models. . . . .                                                                                                                                                                                                                                           | 159 |

| 5.6  | Extracted SAC statistics for a Transformer module (Layer 15) in LLaMA v3.2-1B. .                                                                                                                                                                                                                                       | 163 |

DEDICATED TO MY GRANDPARENTS

# Acknowledgments

First and foremost, I want to thank my advisor, **Stratos Idreos**, for giving me the space to explore and the structure to stay grounded. His trust let me chase ideas I cared about, and his clarity helped shape them into something real. I will always remember our late-night meetings and the conversations that went beyond research, touching on what it means to become a well-rounded researcher and person. I have learned a lot from how he thinks, and even more from how he motivates and instills unwavering belief. No matter how many things were close to deadlines, including paper submissions, presentations, and defense preparation, he never discouraged me. Instead, he showed even more enthusiasm and pushed me to do better.

I am also grateful to my thesis committee: **Prof. David Brooks**, **Prof. H. T. Kung**, and **Prof. Todd Zickler**. Thank you for your time, thoughtful questions, and constructive feedback. Your insights helped make this work more rigorous, complete, and grounded.

To my labmates and collaborators, thank you for the whiteboard debates, the bug hunts, and the shared momentum. This work reflects your input more than you know. **Andrew, Emma, Sophie, Costin, Alicia, Glen, and Vlad**, your energy, curiosity, and intelligence constantly inspired me, and I learned a lot from our collaboration. **Brian, Utku, Qitong, Wasay, Subarna, Subhadeep, Suvam, and Arpita**, thank you for mentoring me, guiding me, and spending countless hours in brainstorming sessions and technical deep dives. Our random philosophical and geeky conversations reminded me that I was in the right place with the right people and made research genuinely fun.

To my collaborators at PyTorch, **Animesh, Gokul, Xuan, Wanchao, Tianyu, Less, and Wei**, thank you for helping push my research into production and for working with me to scale up prototypes into full systems.

To my friends, thank you for your patience, encouragement, and the late-night conversations that had nothing to do with research. You helped me reset when I needed it and made space for this work when I could not. To my friends in Boston, **Greta, Shivam, Charuvi, Moulshree, Radhika, Veronica, Vanessa, Ricky, and Javi**, thank you for making the city feel like home, listening to my rants and complaints, cooking for me, and making Boston winters not only bearable but joyful. I will always remember our Thanksgiving celebrations and hope we continue the tradition. To my PhD compatriot and best roommate **Harsh**, thank you for being patient, wise, and mature, and for throwing the best parties. You were a true one-stop solution for all my worries.

To the friends and their partners I met during my time at IISc, **Stanly, Ajinkya, Bhushan, Vysakh, Swapnil, Bhagyashree, and Divya**, thank you for supporting me through personal ups

and downs, always believing in me, hyping me up, and being there on long video calls whenever I needed you. Even after moving away, I never felt like I left you. We have grown together from naive college graduates to industry engineers and researchers. The journey has been incredible to share with you.

To **Rucha**, thank you for motivating me to pursue a PhD and for giving me an early glimpse into the world of research. You taught me to aim higher and helped instill ambition in me when it mattered most.

To **Prof. Jayant Haritsa**, **Prof. Matthew Jacob**, and **Prof. Bhavana Kanukurthi**, thank you for your guidance during my time at IISc. You helped me build a solid foundation and taught me how to think and do research. **Prof. Jayant**, you were instrumental in guiding me towards my master's dissertation, which served as a stepping stone toward securing a PhD position with Stratos.

To **Dr. Karthik Ramachandra**, with whom I spent an amazing six months at Microsoft Research, thank you for guiding me through my first research paper, helping me secure my first patent, and giving me a thorough exposure to industry research.

To my friends **Vivek, Laura, Tejashri, and Leena**, thank you for filling my life with love, laughter, vacations, incredible dinners, and for helping me find joy beyond academia. Traveling, hiking, working out, and camping with you brought me balance and perspective. Thank you for helping me navigate real-life decisions, for your advice, and for giving me a safe space to open up.

To my mentor **Rajesh Singh Vats**, who coached me for the GATE examination, thank you for helping me secure a spot at IISc, which completely transformed my career trajectory. I would not have the opportunities I have today without your support.

To my undergraduate thesis advisor and mentor **Prof. Tanuja Sarode**, thank you not only for guiding my thesis but also for nurturing leadership abilities and soft skills that have helped me throughout my career.

To my parents, thank you for being steady through it all. You never needed to understand the details to believe in the effort. Your belief in me, your sacrifices, and your strength meant I never had to look elsewhere for motivation.

To my sister **Manasi**, thank you for your unconditional support and for being my best friend, mentor, and second mother all at once.

To my cousin and best friend **Archit**, thank you for being my wise little brother. You reminded me to take life one step at a time and always told me what I needed to hear, that everything will be fine.

To my cousins and their partners **Mayuri, Sagar, Neeraj, and Seema**, thank you for giving me family abroad and for being a constant source of warmth and support.

To my cousins in India, **Yashodhan, Vidya, Risha, and Rutvi**, thank you for always being there for me and staying connected despite the distance.

And to my aunts and uncles, thank you for your encouragement, love, and belief in me over the years. Your presence, near or far, has always mattered.

# 1

## Introduction

### 1.1 MOTIVATION

AI models are the driving force behind a wide range of applications. Large Language Models (LLMs) (Devlin, 2018; Liu et al., 2019; Radford et al., 2019; Chowdhery et al., 2023; Anil et al., 2023; Achiam et al., 2023; Dubey et al., 2024; Jiang et al., 2024; Abdin et al., 2024) have been the driving force behind the advancement of natural language processing (NLP) applications spanning

language translation, content/code generation, conversational AI, text data analysis, creative writing and art, education, and research, etc. At the same time Large Vision Models (LVMs) (Ilharco et al., 2021; Rombach et al., 2021; Li et al., 2024a; Meta AI, 2024; Labs, 2024) have been central to progress in image recognition, visual alignment, multimodal interaction, and prompt-based image generation.

**Training AI models is computationally expensive.** Achieving state-of-the-art performance in large language models (LLMs) requires extreme computational scale and investment. For example, Llama 3.1 was trained with 405 billion parameters on 15 trillion tokens, consuming 30.84 million GPU hours across 16,000 H100 GPUs (Dubey et al., 2024), while Google’s PaLM used 540 billion parameters and 0.8 trillion tokens, requiring 9.4 million TPU hours across 6,144 TPUs (Chowdhery et al., 2023). These models showcase remarkable capabilities in language understanding and generation, but also highlight the steep memory, compute, and time requirements needed to train at this scale. As models continue to grow in size and complexity, these costs extend across domains, often reaching millions of GPU hours and significant financial overhead. Reducing the time, resource usage, and cost of training has become a critical challenge for sustainable and scalable AI development.

**Distributed training is essential to scale large models across thousands of GPUs, with no single recipe being universally optimal.** For example, Llama 3.1 (405B) was trained using 4D parallelism comprising 8-way Tensor, 16-way Context, 16-way Pipeline, and 8-way Fully Sharded Data Parallelism across 16,000 GPUs. In contrast, PaLM (540B) was trained on 6,144 TPUs using 3D parallelism with 12-way Tensor, 256-way Fully Sharded Data, and 2-way Data Parallelism. Despite their similar scale, the two models used distinct strategies due to differences in architecture, size, and hardware.

**Efficient distributed training requires stacking several techniques, often with complex trade-offs.** Training large language models (LLMs) at scale is a daunting task that requires a delicate

balance of parallelism, computation, and communication, all while navigating intricate memory and computation trade-offs. The massive resources required for training make it prone to GPU failures, underscoring the need for efficient recovery mechanisms and checkpointing strategies to minimize downtime (Eisenman et al., 2022; Wang et al., 2023; Gupta et al., 2024; Maurya et al., 2024; Wan et al., 2024). To optimize resource utilization and achieve elastic scalability, it is crucial to combine multiple parallelism techniques, including Data Parallel (DDP, HSDP and FSDP) (Li et al., 2020; Rajbhandari et al., 2020; Zhang et al., 2022a; Zhao et al., 2023), Tensor Parallel (TP) (Narayanan et al., 2021; Wang et al., 2022; Korthikanti et al., 2023), Context Parallel (CP) (Liu et al., 2023; Liu & Abbeel, 2024; NVIDIA, 2023; Fang & Zhao, 2024), and Pipeline Parallel (PP) (Huang et al., 2019b; Narayanan et al., 2019, 2021; Tang et al., 2024b). By stacking these parallelisms with memory and computation optimization techniques, such as activation recomputation (Chen et al., 2016; Korthikanti et al., 2023; He & Yu, 2023; Purandare et al., 2023), mixed precision training (Micikevicius et al., 2018, 2022), and deep learning compilers (Bradbury et al., 2018; Yu et al., 2023; Li et al., 2024b; Ansel et al., 2024b), it is possible to maximize hardware utilization.

**Discovering an effective training recipe requires expert intuition and extensive experimentation.** While existing systems support a broad range of distributed training techniques, they also expose a large number of configuration options, including parallelism dimensions, sharding strategies, precision modes, and memory trade-offs. Choosing the right combination of techniques, referred to as a training recipe, for a given model, data batch, hardware setup, and performance objective is highly non-trivial. This process is highly context-dependent and typically demands expert intuition, deep system knowledge, and substantial iterative experimentation.

**Training under sub-optimal configurations can significantly increase training time and resource consumption.** Even when frameworks support a wide range of optimization techniques, using them ineffectively can be extremely costly. Consider our earlier examples: LLaMA 3.1 (405B) and PaLM (540B), which consumed 30.84 million GPU hours and 9.4 million TPU hours, re-

**Table 1.1:** Cost and experiment counts per model size (in k\$) for 3,306 experiments, resulting in a total estimated cost of \$469.17K.

| Model (B) | Cost (k\$) | Experiments per node config |     |     |     |     |     |    |

|-----------|------------|-----------------------------|-----|-----|-----|-----|-----|----|

|           |            | 1                           | 2   | 4   | 8   | 16  | 32  | 64 |

| 1.34      | 107.34     | 65                          | 120 | 127 | 149 | 158 | 111 | 78 |

| 3.57      | 119.78     | 63                          | 117 | 126 | 148 | 176 | 118 | 94 |

| 8.86      | 119.95     | 61                          | 116 | 122 | 145 | 176 | 122 | 93 |

| 80.0      | 122.10     | 57                          | 87  | 125 | 150 | 185 | 122 | 95 |

spectively. Hypothetically, if these models were trained using configurations that are just 10 to 25% slower than an optimally tuned setup [Tazi et al. \(2025\)](#), this would result in an additional 3.08 to 7.71 million GPU hours or 0.94 to 2.35 million TPU hours. These inefficiencies translate directly into substantial financial costs and increased environmental impact due to unnecessary energy consumption.

**Crafting the best training recipe requires costly exploration of the performance space.**

Identifying an optimal training recipe, which consists of a combination of parallelism strategies, memory optimizations, and precision settings for a given model, dataset, and hardware configuration, is a complex and expensive process. The configuration space is large and filled with highly sensitive parameters that must be tuned to balance cost, accuracy, communication overhead, and computational efficiency. Even with modern tooling, this remains an iterative trial-and-error process that requires multiple full or partial training runs on GPU clusters. Each run involves job scheduling, execution, metric collection, and debugging. Frequent runtime failures, such as out-of-memory errors, further increase overhead. As models grow and training scales to hundreds or thousands of GPUs, this level of empirical exploration becomes increasingly impractical and motivates the need for automated and simulation-driven approaches.

**Case Study: Exhaustive benchmarking for training configuration selection is prohibitively expensive.**

**Figure 1.1:** Huggingface performance benchmarking of 1,728 out of 3,306 training runs reveals significant variance in throughput and peak memory consumption, highlighting the impact of training configurations.

To illustrate the cost and complexity of empirical exploration, we highlight a performance benchmarking study conducted by Huggingface (Tazi et al., 2025), which evaluated training configurations for LLaMA models of various sizes (1.34B, 3.57B, 8.86B, and 80B parameters). The study maintained a fixed global batch size of 256 and sequence length of 4096, and systematically varied key parameters such as the number of nodes (ranging from 1 to 64), degrees of data parallelism (1 to 256), tensor parallelism (1 to 32), pipeline parallelism (1 to 128), gradient accumulation steps (1 to 256), micro-batch size (1 to 256), and ZeRO sharding strategies (stage 0 and 1). A total of 3,306 configurations were benchmarked on a cluster with up to 512 NVIDIA H100 GPUs (8 GPUs per node), with 1,728 runs completing successfully and 1,578 failing due to crashes or out-of-memory (OOM) errors.

The results reveal three major insights. First, training performance and memory efficiency are highly sensitive to configuration choices. As shown in Figure 1.1, throughput and peak memory usage vary significantly across configurations. Trade-offs are inherent; for example, activation checkpointing reduces memory usage at the cost of recomputation, while tensor or fully shared data parallelism improves memory distribution but increases synchronization overhead. Inefficient overlap of computation and communication can further degrade performance, making configuration selection

highly non-trivial.

Second, failure modes such as OOM errors are frequent and offer little diagnostic value. Out of 3,306 runs, 1,578 failed due to memory exhaustion, resulting in substantial waste of resources and no actionable insights for tuning future configurations.

Third, the financial cost of empirical benchmarking is substantial. The study incurred an estimated total cost of \$469.17K, assuming a cost of \$98.5 per node-hour\* and a runtime of five minutes per experiment. Table 1.1 provides a detailed breakdown by model size and node count.

Despite fixing multiple parameters, including batch size, sequence length, precision mode, and activation checkpointing strategy, the study required thousands of runs to explore only a narrow slice of the full configuration space. Expanding this search to include additional models and optimization techniques would drastically increase both cost and complexity, reinforcing the need for automated and simulation-based approaches to training configuration selection.

**Current Distributed Training Frameworks Fall Short: Gaps in Composability, Breadth, Flexibility, and Efficiency.** Exacerbating the challenge of discovering an optimal training recipe is the difficulty of engineering an efficient implementation for a given configuration. Despite advances in distributed training techniques, existing frameworks struggle to support their full breadth and composability. Most systems are non-composable, making it hard to stack multiple parallelism strategies alongside memory and compute optimizations, which limits both efficiency and design space exploration. Their architectures often lack flexibility and modularity, impeding integration of new techniques, hardware targets, and evolving software optimizations. Many frameworks underutilize advanced hardware features, offer limited support for customizable checkpointing, and exhibit sub-optimal GPU efficiency. In production, they lack scalable distributed checkpointing, robust failure recovery, and effective debugging tools. Additionally, many rely on poorly main-

---

\*Cost estimate based on AWS EC2 p5.48xlarge (8×H100) on-demand pricing ([CloudPrice.net, 2025](#)). The total expenditure was estimated using the formula: Cost = Number of Experiments × Nodes × 98.5 × ( $\frac{5}{60}$ ), assuming five minutes per experiment.

tained external dependencies and fail to fully leverage PyTorch’s native optimizations, compiler infrastructure, and kernel support, leading to inefficiencies and compatibility challenges across the stack.

## 1.2 THESIS PROBLEM AND THESIS STATEMENT

### 1.2.1 PROBLEM

Given a specific training context consisting of a model architecture, dataset, and hardware platform, automatically and efficiently identify the empirically optimal distributed training configuration, which spans parallelism strategies, memory optimizations, and precision settings, and generate a corresponding implementation that maximizes throughput while satisfying hardware constraints.

### 1.2.2 STATEMENT

This thesis introduces LEGOAI, a system that transforms distributed AI training into an automated, scalable, and modular process. Given a model, dataset, and hardware configuration, LEGOAI automatically selects the optimal distributed training configuration and generates a production-ready implementation that scales to thousands of GPUs. At its core, LEGOAI serves as a synthesis engine: it decomposes state-of-the-art training strategies into modular, composable design principles and unifies them within a single coherent framework. In doing so, LEGOAI exposes a vast configuration space that comprises not only existing state-of-the-art algorithms but also entirely new designs beyond them. Through high-fidelity simulation, it predicts memory usage and runtime without requiring execution, enabling fast and safe exploration of the configuration space. Finally, for the empirically optimal configuration, it synthesizes an efficient and scalable implementation.

LEGOAI consists of two core subsystems:

1. **TORCHTITAN**, a unified and production-grade distributed training framework that supports modular and composable four-dimensional parallelism with elastic scaling. TORCHTITAN consolidates advanced parallelism strategies into a single abstraction that simplifies implementation, benchmarking, and the development of new training algorithms.

2. **TORCHSIM**, a simulation-based predictor that estimates memory usage and runtime for arbitrary training configurations. TORCHSIM combines analytical models with learned cost functions to emulate GPU execution at the operator level, generalizing across model architectures, parallelism schemes, hardware types, and interconnect topologies.

To demonstrate the extensibility of LEGOAI and its capability to support new research, we introduce AUTO-SAC, a scalable algorithm that uses TORCHSIM’s fine-grained predictions to generate optimal selective activation checkpointing (SAC) strategies. Integrated into TORCHTITAN, AUTO-SAC highlights LEGOAI’s ability to unify simulation, synthesis, and deployment within a single system.

### 1.3 TORCHTITAN: A UNIFIED, MODULAR, COMPOSABLE, AND SCALABLE DISTRIBUTED TRAINING FRAMEWORK

Although distributed training techniques have progressed significantly, current frameworks fall short of generating efficient implementations for arbitrary distributed training configurations. They are limited in integration, usability, and extensibility, constraining their utility in both research and production workflows.

### 1.3.1 EXISTING SYSTEMS STRUGGLE TO SUPPORT FULL BREADTH AND COMPOSABILITY FOR DISTRIBUTED TRAINING

Several frameworks provide APIs for building distributed training workflows, including Megatron-LM (Narayanan et al., 2021), DeepSpeed (Rasley et al., 2020), veScale (Inc., 2024), Slapo (Chen et al., 2023), and PyTorch Distributed (Paszke et al., 2019; Meta Platforms, Inc., 2024). However, these systems exhibit significant limitations in flexibility, integration, and scalability. Megatron-LM requires intrusive model modifications to work with TransformerEngine, lacks seamless integration of Fully Sharded Data Parallel (FSDP) with tensor and pipeline parallelism, and does not support advanced pipeline schedules to reduce computation overhead. DeepSpeed depends on Megatron-LM for tensor and context parallelism and offers only limited support for FSDP and advanced pipeline scheduling. veScale does not support FSDP, context parallelism, selective activation checkpointing, Float8 training, or the PyTorch `torch.compile` backend, and provides only three pipeline schedules in contrast to the six available in TORCHTITAN. Slapo introduces a schedule language to express training optimizations such as three-dimensional parallelism and supports progressive application of high-level transformations, but still lacks full integration with diverse parallelism and optimization strategies. These limitations restrict composability and hinder systematic exploration of the training configuration space, both of which are critical for scalable and efficient model training.

### 1.3.2 TOWARD COMPOSABLE DISTRIBUTED TRAINING: DTENSOR AND DEVICEMESH AS FIRST-CLASS PRIMITIVES

**Root cause: Lack of unified tensor and device abstractions across the stack.** A central reason for the non-composability and rigidity of existing distributed training frameworks is the absence of unified tensor and device abstractions that span the entire software stack. Without such foundational

components, parallelism strategies, checkpointing mechanisms, and performance optimizations remain fragmented and ad hoc. This fragmentation limits modularity, restricts scalability, and complicates extensibility, making it difficult to build systems that can flexibly combine multiple training techniques or adapt to evolving hardware environments.

**Using DTensor and DeviceMesh as foundational building blocks.** To address this, we adopt PyTorch’s Distributed Tensor (DTensor) and DeviceMesh as core primitives for structuring distributed computation. The DeviceMesh provides a logical organization of the compute cluster by arranging devices into a multi-dimensional grid, where each dimension corresponds to a distinct parallelism strategy. It manages process group creation and device communication across these dimensions in a unified and scalable manner.

DTensor is a distributed tensor that is sharded along one or more dimensions of the DeviceMesh and encodes its sharding specification. It supports sharding propagation, which automatically carries sharding metadata through tensor operations. This enables the composition of multiple forms of parallelism without requiring manual tracking or user intervention. When a sharded tensor is used as input, output tensors inherit the correct sharding behavior by default. DTensor also supports collective operations in sharded contexts, preserving semantic correctness and enabling reliable, deterministic execution across devices.

### 1.3.3 SOLUTION: REDESIGNING DISTRIBUTED TRAINING FROM FIRST PRINCIPLES

TORCHTITAN’s key contribution is the unification of distributed parallelism and optimization techniques within a cohesive and extensible framework. By building on and extending PyTorch’s DTensor and DeviceMesh abstractions (PyTorch Community, 2023b), TORCHTITAN provides a unified representation of distributed training that simplifies the composition of parallelism strategies and preserves consistent single-device semantics through principled sharding primitives. In contrast to prior systems that rely on rigid or task-specific implementations, TORCHTITAN offers a

systematic foundation for distributed execution. This enables rigorous exploration of configuration options, robust benchmarking of existing methods, and the discovery of new strategies across the broader design space.

`TORCHTITAN` is a full-fledged distributed training system for large language models (LLMs), not merely a collection of isolated techniques. Its modular and extensible architecture supports seamless integration of four-dimensional parallelism, advanced optimization techniques, and scalable checkpointing mechanisms, all while leveraging native PyTorch capabilities. The system is designed for production-scale training on thousands of GPUs, while also reducing integration complexity and accelerating experimentation, setting a new standard for scalable, composable, and flexible distributed training.

Finally, `TORCHTITAN` serves as an experimental testbed that enables users to curate, benchmark, and compare multiple training recipes for the same model and hardware configuration. Its strength lies in its ability to comprehensively capture the distributed training configuration space, allowing principled evaluation across a broad spectrum of strategies to identify the most effective ones.

#### 1.4 `TORCHSIM`: HIGH FIDELITY RUNTIME AND MEMORY ESTIMATION FOR DISTRIBUTED TRAINING

While `TORCHTITAN` allows users to curate and evaluate the training recipes by mixing and matching different configurations, users still need to find the best training configuration for launching their training run.

#### 1.4.1 THE HOLY GRAIL FOR AI TRAINING AT SCALE: ACCURATE RUNTIME AND MEMORY ESTIMATION.

**Accurate Cost Estimation as a Foundation for Training Recipe Search** If it were possible for machine learning practitioners to estimate the memory consumption and runtime of a training configuration before execution, it would fundamentally change how large-scale model training is conducted. First, accurate memory estimation would allow immediate detection of configurations likely to fail due to out-of-memory errors, preventing wasted time and resources. Second, accurate runtime prediction would enable practitioners to select the fastest configuration among those that satisfy memory constraints. Together, these capabilities would eliminate the need for trial-and-error experimentation, allowing researchers and engineers to assess feasibility and performance upfront, before committing expensive compute resources, time, and cloud budget.

**The complexity of end-to-end training cost estimation at scale.** Despite its transformative potential, accurate cost estimation is extremely challenging due to the intricate nature of distributed training systems. First, training performance depends heavily on the selected parallelism strategy, such as data, tensor, pipeline, or hybrid parallelism, each introducing different communication patterns and synchronization overheads that influence runtime in non-trivial ways. Second, hardware heterogeneity further complicates prediction. GPU architecture, memory bandwidth, interconnect topology, and hardware-specific scheduling behaviors all impact both computational throughput and communication efficiency.

Third, memory usage is governed by tensor liveness, which varies significantly across different operator sequences and training strategies. Constructing a general analytical model that accounts for memory lifetimes across arbitrary training configurations is infeasible. Finally, modern training frameworks introduce dynamic runtime optimizations such as overlapping communication and computation through asynchronous execution streams. These behaviors evolve rapidly with

framework updates, making theoretical performance modeling brittle and unreliable at scale. As a result, practical and accurate cost estimation requires a simulation-based approach that can emulate real-world execution while accounting for the full complexity of the training stack.

#### 1.4.2 LIMITATIONS OF EXISTING RUNTIME AND MEMORY ESTIMATION APPROACHES

Existing runtime estimation techniques are largely limited to simplified single-GPU or kernel-level settings [Geoffrey et al. \(2021\)](#); [Lee et al. \(2025a\)](#); [Zhang et al. \(2022b\)](#); [Li et al. \(2022\)](#), and fail to capture the complexity of distributed training. Communication models often neglect critical system factors, including multi-tier network topologies, collective communication algorithms, and the impact of straggler delays [Lee et al. \(2025b\)](#); [Won et al. \(2023\)](#); [Mohammad et al. \(2017\)](#). Moreover, accurate end-to-end performance prediction requires modeling the *computation–communication overlap* introduced by advanced distributed training strategies such as Fully Sharded Data Parallel (FSDP), Tensor Parallelism (TP), Pipeline Parallel (PP), and Context Parallelism (CP). To the best of our knowledge, no existing work faithfully simulates these algorithms, leaving accurate runtime estimation an unsolved problem.

Similarly, memory estimation tools are primarily profiling-based and operate *post hoc* [Shi & DeVito \(2023\)](#); [pyt \(2025a\)](#), offering no predictive insights into the memory impact of training configurations or the ability to prevent Out-of-Memory (OOM) errors proactively. Analytical techniques for estimating peak memory usage [Gao et al. \(2020\)](#); [Narayanan et al. \(2021\)](#) are difficult to maintain and often inaccurate due to the opaque and evolving internals of modern training frameworks. Other single-GPU tools [Yu et al. \(2020\)](#); [Su et al. \(2024\)](#) require actual execution and do not generalize to distributed contexts; they also lack detailed memory attribution and breakdown. To the best of our knowledge, no existing method provides accurate, predictive memory estimation for full-scale distributed training.

### 1.4.3 SOLUTION: UNIFIED MODELING OF LARGE-SCALE AI TRAINING HARDWARE-CONSCIOUS LEARNED AND ANALYTICAL ESTIMATION AND DISTRIBUTED GPU EXECUTION SIMULATION

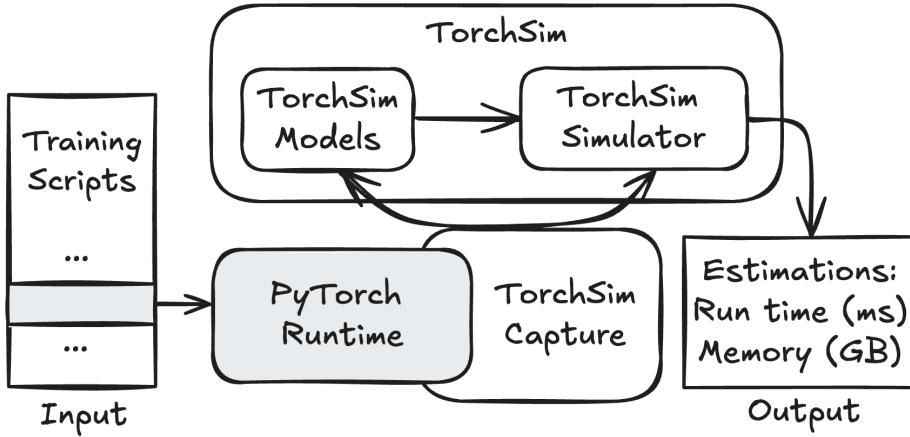

We introduce **TORCHSIM**, a predictive tool for estimating runtime and memory consumption in distributed deep learning training workloads without requiring GPU execution.

**TORCHSIM** combines hardware-aware compute models with communication models that are sensitive to topology, algorithmic structure, and collective communication patterns to accurately predict operator-level execution times. It employs a detailed simulator that closely replicates the multi-stream GPU execution model, capturing compute–communication overlap, exposed communication phases, and synchronization overheads to support accurate end-to-end runtime estimation.

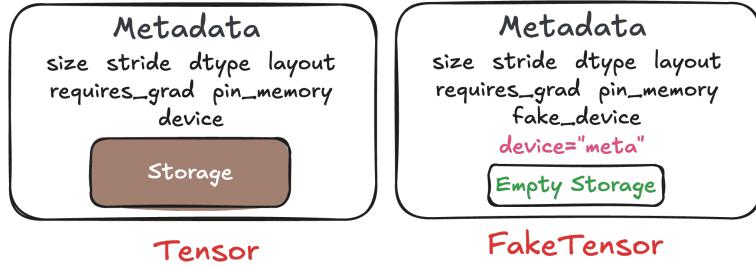

For memory prediction, **TORCHSIM** tracks tensor memory usage at operator-level granularity without allocating memory, and emulates memory consumed by distributed collective operations. By mimicking PyTorch’s memory management and execution semantics, **TORCHSIM** can simulate realistic training behavior, including effects from sharding, activation recomputation, and communication buffering.

This capability allows users to evaluate training configurations and cluster topologies before execution, enabling principled design decisions and eliminating the need for costly empirical benchmarking. **TORCHSIM** serves as the foundation for system-level optimization in **LEGOAI**, making accurate performance prediction a first-class component of the distributed training pipeline.

### 1.5 AUTO-SAC: ENHANCING THE COMPUTE–MEMORY EFFICIENCY TRADE-OFF IN DISTRIBUTED TRAINING

To demonstrate the extensibility of **LEGOAI** and its ability to drive principled system innovation, we develop **AUTO-SAC**, a principled and scalable algorithm for generating selective activation

checkpointing (SAC) policies. SAC is a widely adopted technique for reducing peak memory usage by selectively recomputing intermediate activations during the backward pass. While existing approaches are either manually configured or use limited automation, they often fail to support fine-grained control or adapt to realistic hardware constraints. AUTO-SAC addresses these challenges by leveraging TORCHSIM’s operator-level runtime and memory estimates, not only for simulation, but to empirically construct memory–compute trade-off curves and guide memory-aware optimization.

AUTO-SAC operates in two stages. At the global level, we formulate a memory-constrained Integer Linear Program (ILP) that determines which modules should apply SAC and how much activation memory to discard. This optimization is driven by piecewise-linear approximations of memory–recomputation trade-off curves, generated from TORCHSIM’s operator-level performance predictions. At the local level, we generate fine-grained SAC policies for each selected module using one of three algorithms: a greedy heuristic, a knapsack-based dynamic programming solver, or a local ILP for exact operator-level optimization. These local solvers balance recomputation cost with memory savings, enabling precise activation discard decisions under module-level constraints.

The key insight behind AUTO-SAC is to decompose the SAC policy generation problem into a two-level hierarchy. The global module-level ILP enables tractable coordination under memory budgets across the model, while the local per-module optimization enables fine-grained control over which activations to retain or recompute. This hierarchical approach ensures that SAC policies are both globally coordinated and locally optimized.